mosfet驅(qū)動(dòng)

mosfet驅(qū)動(dòng),跟雙極性晶體管相比,一般認(rèn)為使MOS管導(dǎo)通不需要電流,只要GS電壓高于一定的值,就可以了。這個(gè)很容易做到,但是,我們還需要速度。

在MOS管的結(jié)構(gòu)中可以看到,在GS,GD之間存在寄生電容,而MOS管的驅(qū)動(dòng),實(shí)際上就是對(duì)電容的充放電。對(duì)電容的充電需要一個(gè)電流,因?yàn)閷?duì)電容充電瞬間可以把電容看成短路,所以瞬間電流會(huì)比較大。選擇/設(shè)計(jì)MOS管驅(qū)動(dòng)時(shí)第一要注意的是可提供瞬間短路電流的大小。

第二注意的是,普遍用于高端驅(qū)動(dòng)的NMOS,導(dǎo)通時(shí)需要是柵極電壓大于源極電壓。而高端驅(qū)動(dòng)的MOS管導(dǎo)通時(shí)源極電壓與漏極電壓(VCC)相同,所以這時(shí) 柵極電壓要比VCC大4V或10V。如果在同一個(gè)系統(tǒng)里,要得到比VCC大的電壓,就要專門(mén)的升壓電路了。很多馬達(dá)驅(qū)動(dòng)器都集成了電荷泵,要注意的是應(yīng)該 選擇合適的外接電容,以得到足夠的短路電流去驅(qū)動(dòng)MOS管。

4V或10V是常用的MOS管的導(dǎo)通電壓,設(shè)計(jì)時(shí)當(dāng)然需要有一定的余量。而且電壓越高,導(dǎo)通速度越快,導(dǎo)通電阻也越小。現(xiàn)在也有導(dǎo)通電壓更小的MOS管用在不同的領(lǐng)域里,但在12V汽車電子系統(tǒng)里,一般4V導(dǎo)通就夠用了。

MOS管的驅(qū)動(dòng)電路及其損失,可以參考Microchip公司的AN799 Matching MOSFET Drivers to MOSFETs。

mosfet驅(qū)動(dòng)的幾個(gè)特別需求

1.低壓應(yīng)用:當(dāng)使用5V電源,這時(shí)候如果使用傳統(tǒng)的圖騰柱結(jié)構(gòu),由于三極管的be有0.7V左右的壓降,導(dǎo)致實(shí)際最終加在gate上的電壓只有4.3V。這時(shí)候,我們選用標(biāo)稱gate電壓4.5V的MOS管就存在一定的風(fēng)險(xiǎn)。 同樣的問(wèn)題也發(fā)生在使用3V或者其他低壓電源的場(chǎng)合。

2.寬電壓應(yīng)用:輸入電壓并不是一個(gè)固定值,它會(huì)隨著時(shí)間或者其他因素而變動(dòng)。這個(gè)變動(dòng)導(dǎo)致PWM電路提供給MOS管的驅(qū)動(dòng)電壓是不穩(wěn)定的。為了讓MOS管在高gate電壓下安全,很多MOS管內(nèi)置了穩(wěn)壓管強(qiáng)行限制gate電壓的幅值。在這種情況下,當(dāng)提供的驅(qū)動(dòng)電壓超過(guò)穩(wěn)壓管的電壓,就會(huì)引起較大的靜態(tài)功耗。

同時(shí),如果簡(jiǎn)單的用電阻分壓的原理降低gate電壓,就會(huì)出現(xiàn)輸入電壓比較高的時(shí)候,MOS管工作良好,而輸入電壓降低的時(shí)候gate電壓不足,引起導(dǎo)通不夠徹底,從而增加功耗。

3.雙電壓應(yīng)用:在一些控制電路中,邏輯部分使用典型的5V或者3.3V數(shù)字電壓,而功率部分使用12V甚至更高的電壓。兩個(gè)電壓采用共地方式連接。這就提出一個(gè)要求,需要使用一個(gè)電路,讓低壓側(cè)能夠有效的控制高壓側(cè)的MOS管,同時(shí)高壓側(cè)的MOS管也同樣會(huì)面對(duì)1和2中提到的問(wèn)題。

在這三種情況下,圖騰柱結(jié)構(gòu)無(wú)法滿足輸出要求,而很多現(xiàn)成的MOS驅(qū)動(dòng)IC,似乎也沒(méi)有包含gate電壓限制的結(jié)構(gòu)。

一個(gè)相對(duì)通用的電路來(lái)滿足這三種需求。

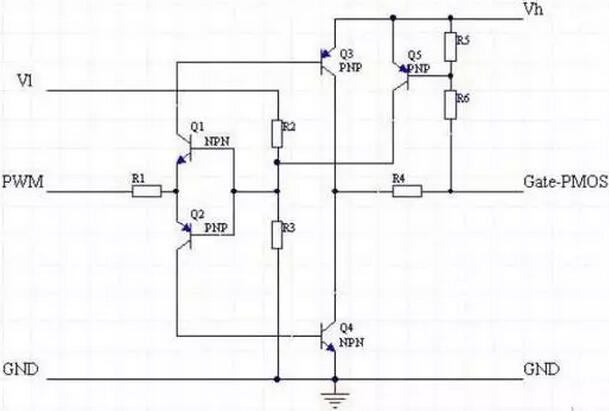

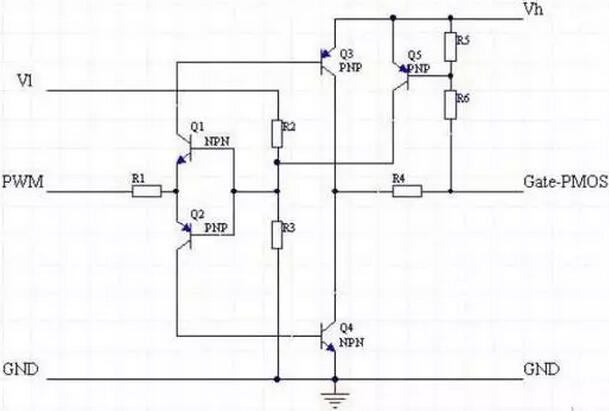

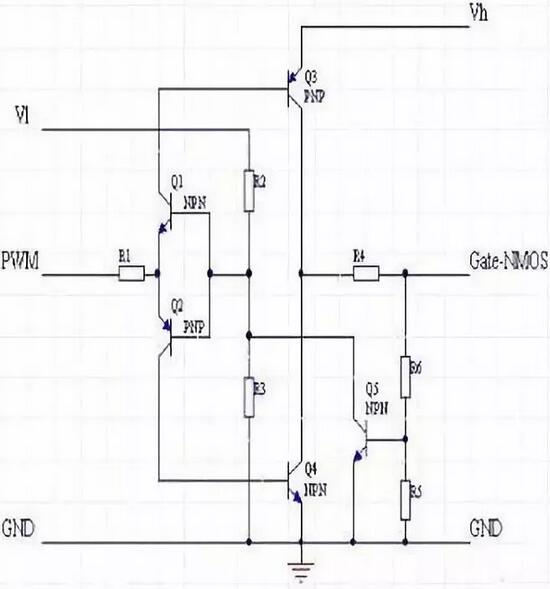

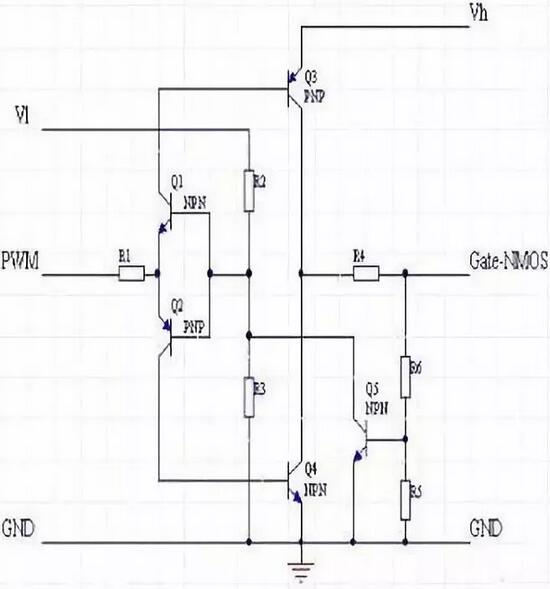

電路圖如下:

用于NMOS的驅(qū)動(dòng)電路

用于POMS的驅(qū)動(dòng)電路

這里我只針對(duì)NMOS驅(qū)動(dòng)電路做一個(gè)簡(jiǎn)單分析:Vl和Vh分別是低端和高端的電源,兩個(gè)電壓可以是相同的,但是Vl不應(yīng)該超過(guò)Vh。Q1和Q2組成了一個(gè)反置的圖騰柱,用來(lái)實(shí)現(xiàn)隔離,同時(shí)確保兩只驅(qū)動(dòng)管Q3和Q4不會(huì)同時(shí)導(dǎo)通。 R2和R3提供了PWM電壓基準(zhǔn),通過(guò)改變這個(gè)基準(zhǔn),可以讓電路工作在PWM信號(hào)波形比較陡直的位置。

Q3和Q4用來(lái)提供驅(qū)動(dòng)電流,由于導(dǎo)通的時(shí)候,Q3和Q4相對(duì)Vh和GND最低都只有一個(gè)Vce的壓降,這個(gè)壓降通 常只有0.3V左右,大大低于0.7V的Vce。 R5和R6是反饋電阻,用于對(duì)gate電壓進(jìn)行采樣,采樣后的電壓通過(guò)Q5對(duì)Q1和Q2的基極產(chǎn)生一個(gè)強(qiáng)烈的負(fù)反饋, 從而把gate電壓限制在一個(gè)有限的數(shù)值。這個(gè)數(shù)值可以通過(guò)R5和R6來(lái)調(diào)節(jié)。

最后,R1提供了對(duì)Q3和Q4的基極電流限制,R4提供了對(duì)MOS管的gate電流限制,也就是Q3和Q4的Ice的限 制。必要的時(shí)候可以在R4上面并聯(lián)加速電容。

這個(gè)電路提供了如下的特性:

1,用低端電壓和PWM驅(qū)動(dòng)高端MOS管。

2,用小幅度的PWM信號(hào)驅(qū)動(dòng)高gate電壓需求的MOS管。

3,gate電壓的峰值限制

4,輸入和輸出的電流限制

5,通過(guò)使用合適的電阻,可以達(dá)到很低的功耗。

6,PWM信號(hào)反相。NMOS并不需要這個(gè)特性,可以通過(guò)前置一個(gè)反相器來(lái)解決。

在設(shè)計(jì)便攜式設(shè)備和無(wú)線產(chǎn)品時(shí),提高產(chǎn)品性能、延長(zhǎng)電池工作時(shí)間是設(shè)計(jì)人員需要面對(duì)的兩個(gè)問(wèn)題。DC-DC轉(zhuǎn)換器具有效率高、輸出電流大、靜態(tài)電流小等優(yōu)點(diǎn),非常適用于為便攜式設(shè)備供電。目前DC-DC轉(zhuǎn)換器設(shè)計(jì)技術(shù)發(fā)展主要趨勢(shì)有:

(1)高頻化技術(shù):隨著開(kāi)關(guān)頻率的提高,開(kāi)關(guān)變換器的體積也隨之減小,功率密度也得到大幅提升,動(dòng)態(tài)響應(yīng)得到改善。小功率DC-DC轉(zhuǎn)換器的開(kāi)關(guān)頻率將上升到兆赫級(jí)。

(2)低輸出電壓技術(shù):隨著半導(dǎo)體制造技術(shù)的不斷發(fā)展,微處理器和便攜式電子設(shè)備的工作電壓越來(lái)越低,這就要求未來(lái)的DC-DC變換器能夠提供低輸出電壓以適應(yīng)微處理器和便攜式電子設(shè)備的要求,這些技術(shù)的發(fā)展對(duì)電源芯片電路的設(shè)計(jì)提出了更高的要求。

首先,隨著開(kāi)關(guān)頻率的不斷提高,對(duì)于開(kāi)關(guān)元件的性能提出了很高的要求,同時(shí)必須具有相應(yīng)的開(kāi)關(guān)元件驅(qū)動(dòng)電路以保證開(kāi)關(guān)元件在高達(dá)兆赫級(jí)的開(kāi)關(guān)頻率下正常工作。其次,對(duì)于電池供電的便攜式電子設(shè)備來(lái)說(shuō),電路的工作電壓低(以鋰電池為例,工作電壓2.5~3.6V),因此,電源芯片的工作電壓較低。

MOS管具有很低的導(dǎo)通電阻,消耗能量較低,在目前流行的高效DC-DC芯片中多采用MOS管作為功率開(kāi)關(guān)。但是由于MOS管的寄生電容大,一般情況下NMOS開(kāi)關(guān)管的柵極電容高達(dá)幾十皮法。這對(duì)于設(shè)計(jì)高工作頻率DC-DC轉(zhuǎn) 換器開(kāi)關(guān)管驅(qū)動(dòng)電路的設(shè)計(jì)提出了更高的要求。

在低電壓ULSI設(shè)計(jì)中有多種CMOS、BiCMOS采用自舉升壓結(jié)構(gòu)的邏輯電路和作為大容性負(fù)載的驅(qū)動(dòng)電路。這些電路能夠在低于1V電壓供電條件下正常工作,并且能夠在負(fù)載電容1~2pF的條件下工作頻率能夠達(dá)到幾十兆甚至上百兆赫茲。本文正是采用了自舉升壓電路,設(shè)計(jì)了一種具有大負(fù)載電容驅(qū)動(dòng)能力的,適合于低電壓、高開(kāi)關(guān)頻率升壓型DC-DC轉(zhuǎn)換器的驅(qū)動(dòng)電路。電路基于Samsung AHP615 BiCMOS工藝設(shè)計(jì)并經(jīng)過(guò)Hspice仿真驗(yàn)證,在供電電壓1.5V ,負(fù)載 電容為60pF時(shí),工作頻率能夠達(dá)到5MHz以上。

自舉升壓結(jié)構(gòu)雙電壓mosfet驅(qū)動(dòng)電路

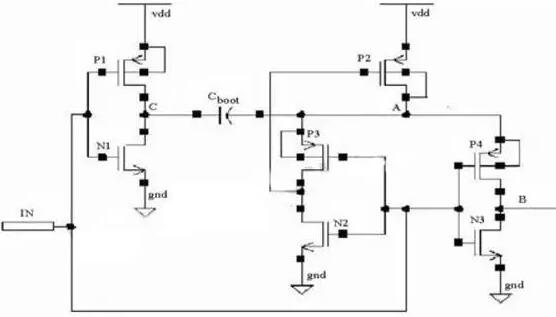

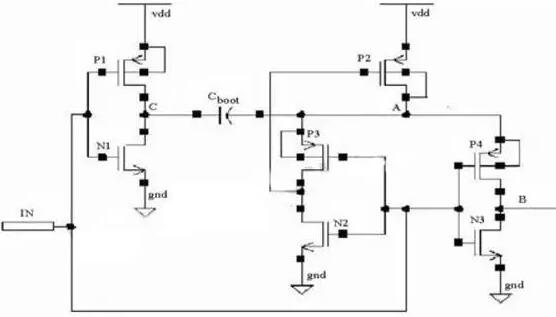

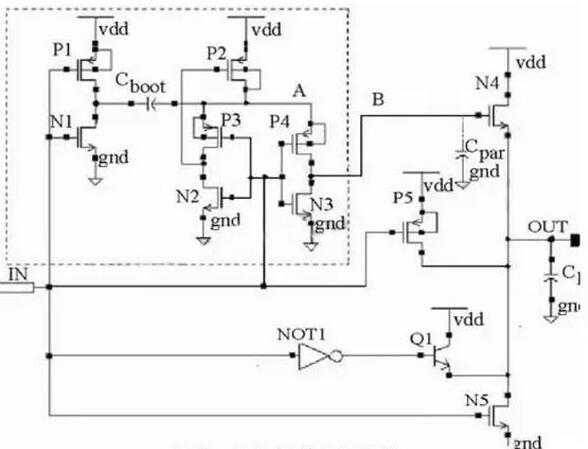

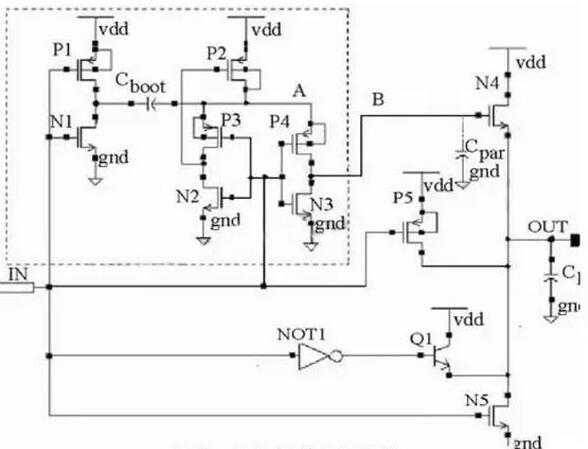

自舉升壓電路的原理圖如圖1所示。所謂的自舉升壓原理就是,在輸入端IN輸入一個(gè)方波信號(hào),利用電容Cboot將A點(diǎn)電壓抬升至高于VDD的電平,這樣就可以在B端輸出一個(gè)與輸入信號(hào)反相,且高電平高于VDD的方波信號(hào)。具體工作原理如下:

自舉升壓電路原理圖

當(dāng)VIN為高電平時(shí),NMOS管N1導(dǎo)通,PMOS管P1截止,C點(diǎn)電位為低電平。同時(shí)N2導(dǎo)通,P2的柵極電位 為低電平,則P2導(dǎo)通。這就使得此時(shí)A點(diǎn)電位約為VDD,電容Cboot兩端電壓UC≈VDD。由于N3導(dǎo)通,P4截止,所以B點(diǎn)的電位為低電平。這段時(shí)間稱為預(yù)充電周期。

當(dāng)VIN變?yōu)榈碗娖綍r(shí),NMOS管N1截止,PMOS管P1導(dǎo)通,C點(diǎn)電位為高電平,約為VDD。同時(shí)N2、N3截止,P3導(dǎo)通。這使得P2的柵極電位升高,P2截止。此時(shí)A點(diǎn)電位等于C點(diǎn)電位加上電容Cboot 兩端電壓,約為2VDD。而且P4導(dǎo)通,因此B點(diǎn)輸出高電平,且高于VDD。這段時(shí)間稱為自舉升壓周期。

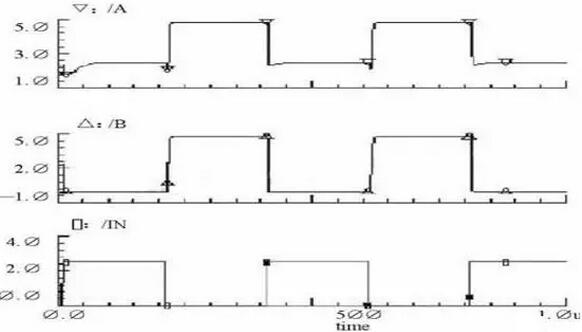

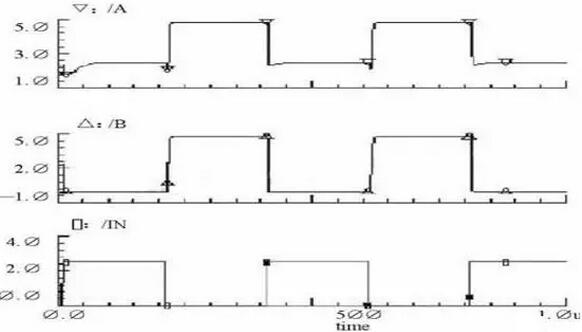

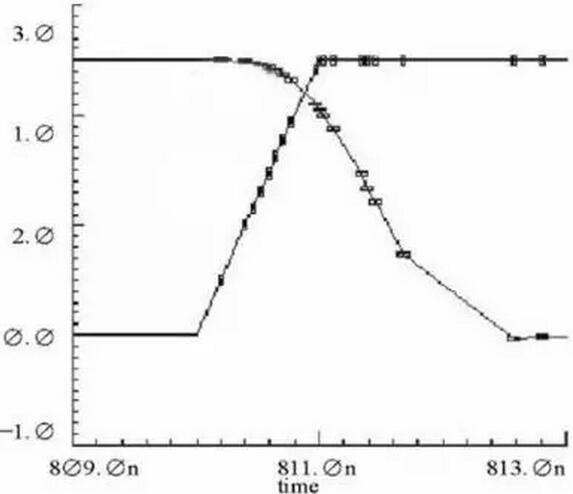

輸入端IN電路與A、B兩點(diǎn)電位關(guān)

實(shí)際上,B點(diǎn)電位與負(fù)載電容和電容Cboot的大小有關(guān),可以根據(jù)設(shè)計(jì)需要調(diào)整。具體關(guān)系將在介紹電路具體設(shè)計(jì)時(shí)詳細(xì)討論。在圖2中給出了輸入端IN電位與A、B兩點(diǎn)電位關(guān)系的示意圖。

驅(qū)動(dòng)電路結(jié)構(gòu)

圖中給出了驅(qū)動(dòng)電路的電路圖。驅(qū)動(dòng)電路采用Totem輸出結(jié)構(gòu)設(shè)計(jì),上拉驅(qū)動(dòng)管為NMOS管N4、晶體管Q1和PMOS管P5。下拉驅(qū)動(dòng)管為NMOS管N5。圖中CL為負(fù)載電容,Cpar為B點(diǎn)的寄生電容。虛線框內(nèi)的電路為自舉升壓電路。

驅(qū)動(dòng)電路原理圖

本驅(qū)動(dòng)電路的設(shè)計(jì)思想是,利用自舉升壓結(jié)構(gòu)將上拉驅(qū)動(dòng)管N4的柵極(B點(diǎn))電位抬升,使得UB>VDD+VTH ,則NMOS管N4工作在線性區(qū),使得VDSN4 大大減小,最終可以實(shí)現(xiàn)驅(qū)動(dòng)輸出高電平達(dá)到VDD。而在輸出低電平時(shí),下拉驅(qū)動(dòng)管本身就工作在線性區(qū),可以保證輸出低電平位GND。因此無(wú)需增加自舉電路也能達(dá)到設(shè)計(jì)要求。

考慮到此驅(qū)動(dòng)電路應(yīng)用于升壓型DC-DC轉(zhuǎn)換器的開(kāi)關(guān)管驅(qū)動(dòng),負(fù)載電容CL很大,一般能達(dá)到幾十皮法,還需要進(jìn)一步增加輸出電流能力,因此增加了晶體管Q1作為上拉驅(qū)動(dòng)管。這樣在輸入端由高電平變?yōu)榈碗娖綍r(shí),Q1導(dǎo)通,由N4、Q1同時(shí)提供電流,OUT端電位迅速上升,當(dāng)OUT端電位上升到VDD-VBE時(shí),Q1截止,N4繼續(xù)提供電流對(duì)負(fù)載電容充電,直到OUT端電壓達(dá)到VDD。

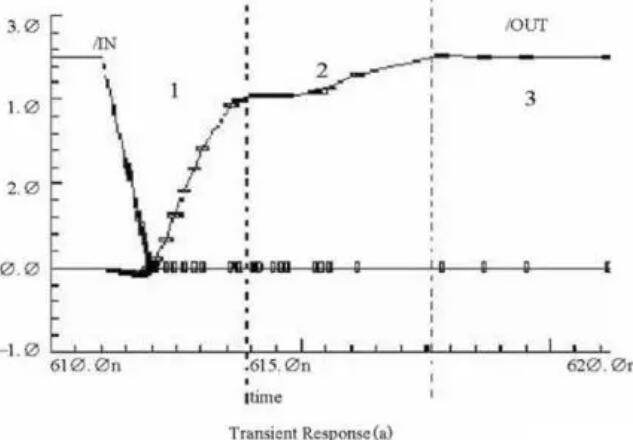

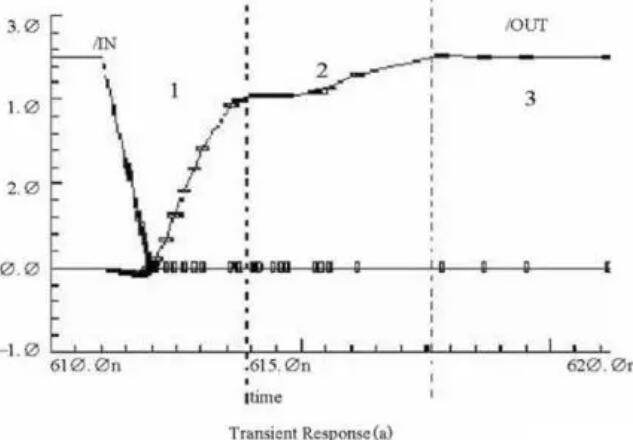

驅(qū)動(dòng)電路傳輸特性瞬態(tài)響應(yīng)

在OUT端為高電平期間,A點(diǎn)電位會(huì)由于電容Cboot 上的電荷泄漏等原因而下降。這會(huì)使得B點(diǎn)電位下降,N4 的導(dǎo)通性下降。同時(shí)由于同樣的原因,OUT端電位也會(huì)有所下降,使輸出高電平不能保持在VDD。為了防止這種現(xiàn)象的出現(xiàn),又增加了PMOS管P5作為上拉驅(qū)動(dòng)管,用來(lái)補(bǔ)充OUT端CL的泄漏電荷,維持OUT端在整個(gè)導(dǎo)通周期內(nèi)為高電平。

驅(qū)動(dòng)電路的傳輸特性瞬態(tài)響應(yīng)在圖4中給出。其中(a)為上升沿瞬態(tài)響應(yīng),(b)為下降沿瞬態(tài)響應(yīng)。從圖4中可以看出,驅(qū)動(dòng)電路上升沿明顯分為了三個(gè)部分,分別對(duì)應(yīng)三個(gè)上拉驅(qū)動(dòng)管起主導(dǎo)作用的時(shí)期。1階段為Q1、N4共同作用,輸出電壓迅速抬升,2階段為N4起主導(dǎo)作,使輸出電平達(dá)到VDD,3階段為P5起主導(dǎo)作用,維持輸出高電平為VDD。而且還可以縮短上升時(shí)間,下降時(shí)間滿足工作頻率在兆赫茲級(jí)以上的要求。

幾種MOSFET驅(qū)動(dòng)電路介紹及分析

不隔離的互補(bǔ)驅(qū)動(dòng)電路

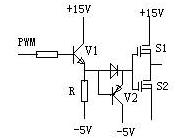

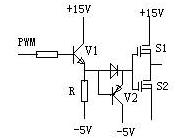

功率MOSFET屬于電壓型控制器件,只要柵極和源極之間施加的電壓超過(guò)其閥值電壓就會(huì)導(dǎo)通。由于MOSFET存在結(jié)電容,關(guān)斷時(shí)其漏源兩端電壓的突然 上升將會(huì)通過(guò)結(jié)電容在柵源兩端產(chǎn)生干擾電壓。常用的互補(bǔ)驅(qū)動(dòng)電路的關(guān)斷回路阻抗小,關(guān)斷速度較快,但它不能提供負(fù)壓,故抗干擾性較差。為了提高電路的抗干 擾性,可在此種驅(qū)動(dòng)電路的基礎(chǔ)上增加一級(jí)有V1、V2、R組成的電路,產(chǎn)生一個(gè)負(fù)壓,電路原理圖如下圖所示。

提供負(fù)壓的互補(bǔ)電路

當(dāng)V1導(dǎo)通時(shí),V2關(guān)斷,兩個(gè)MOSFET中的上管的柵、源極放電,下管的柵、源極充電,即上管關(guān)斷,下管導(dǎo)通,則被驅(qū)動(dòng)的功率管關(guān)斷;反之V1關(guān)斷 時(shí),V2導(dǎo)通,上管導(dǎo)通,下管關(guān)斷,使驅(qū)動(dòng)的管子導(dǎo)通。因?yàn)樯舷聝蓚€(gè)管子的柵、源極通過(guò)不同的回路充放電,包含有V2的回路,由于V2會(huì)不斷退出飽和直至 關(guān)斷,所以對(duì)于S1而言導(dǎo)通比關(guān)斷要慢,對(duì)于S2而言導(dǎo)通比關(guān)斷要快,所以兩管發(fā)熱程度也不完全一樣,S1比S2發(fā)熱嚴(yán)重。

該驅(qū)動(dòng)電路的缺點(diǎn)是需要雙電源,且由于R的取值不能過(guò)大,否則會(huì)使V1深度飽和,影響關(guān)斷速度,所以R上會(huì)有一定的損耗。

隔離的驅(qū)動(dòng)電路

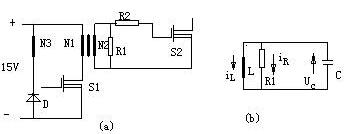

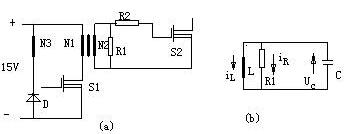

(1)正激式驅(qū)動(dòng)電路。電路原理如下圖(a)所示,N3為去磁繞組,S2為所驅(qū)動(dòng)的功率管。R2為防止功率管柵極、源極端電壓振蕩的一個(gè)阻尼電阻。因不要求漏感較小,且從速度方面考慮,一般R2較小,故在分析中忽略不計(jì)。

正激驅(qū)動(dòng)電路

其等效電路圖如下圖(b)所示脈沖不要求的副邊并聯(lián)一電阻R1,它做為正激變換器的假負(fù)載,用于消除關(guān)斷期間輸出電壓發(fā)生振蕩而誤導(dǎo)通。同時(shí)它還可 以作為功率MOSFET關(guān)斷時(shí)的能量泄放回路。該驅(qū)動(dòng)電路的導(dǎo)通速度主要與被驅(qū)動(dòng)的S2柵極、源極等效輸入電容的大小、S1的驅(qū)動(dòng)信號(hào)的速度以及S1所能 提供的電流大小有關(guān)。由仿真及分析可知,占空比D越小、R1越大、L越大,磁化電流越小,U1值越小,關(guān)斷速度越慢。該電路具有以下優(yōu)點(diǎn):

①電路結(jié)構(gòu)簡(jiǎn)單可靠,實(shí)現(xiàn)了隔離驅(qū)動(dòng)。

②只需單電源即可提供導(dǎo)通時(shí)的正、關(guān)斷時(shí)負(fù)壓。

③占空比固定時(shí),通過(guò)合理的參數(shù)設(shè)計(jì),此驅(qū)動(dòng)電路也具有較快的開(kāi)關(guān)速度。

該電路存在的缺點(diǎn):一是由于隔離變壓器副邊需要噎嗝假負(fù)載防振蕩,故電路損耗較大;二是當(dāng)占空比變化時(shí)關(guān)斷速度變化較大。脈寬較窄時(shí),由于是儲(chǔ)存的能量減少導(dǎo)致MOSFET柵極的關(guān)斷速度變慢。

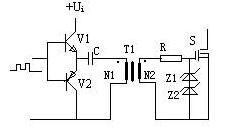

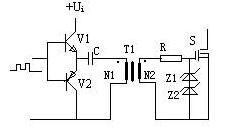

(2)有隔離變壓器的互補(bǔ)驅(qū)動(dòng)電路。如下圖所示,V1、V2為互補(bǔ)工作,電容C起隔離直流的作用,T1為高頻、高磁率的磁環(huán)或磁罐。

隔離變壓器的互補(bǔ)驅(qū)動(dòng)電路

導(dǎo)通時(shí)隔離變壓器上的電壓為(1-D)Ui、關(guān)斷時(shí)為D Ui,若主功率管S可靠導(dǎo)通電壓為12V,而隔離變壓器原副邊匝比N1/N2為12/[(1-D)Ui]。為保證導(dǎo)通期間GS電壓穩(wěn)定C值可稍取大些。該電路具有以下優(yōu)點(diǎn):

①電路結(jié)構(gòu)簡(jiǎn)單可靠,具有電氣隔離作用。當(dāng)脈寬變化時(shí),驅(qū)動(dòng)的關(guān)斷能力不會(huì)隨著變化。

②該電路只需一個(gè)電源,即為單電源工作。隔直電容C的作用可以在關(guān)斷所驅(qū)動(dòng)的管子時(shí)提供一個(gè)負(fù)壓,從而加速了功率管的關(guān)斷,且有較高的抗干擾能力。

但該電路存在的一個(gè)較大缺點(diǎn)是輸出電壓的幅值會(huì)隨著占空比的變化而變化。當(dāng)D較小時(shí),負(fù)向電壓小,該電路的抗干擾性變差,且正向電壓較高,應(yīng)該注意使其 幅值不超過(guò)MOSFET柵極的允許電壓。當(dāng)D大于0.5時(shí)驅(qū)動(dòng)電壓正向電壓小于其負(fù)向電壓,此時(shí)應(yīng)該注意使其負(fù)電壓值不超過(guò)MOAFET柵極允許電壓。所 以該電路比較適用于占空比固定或占空比變化范圍不大以及占空比小于0.5的場(chǎng)合。

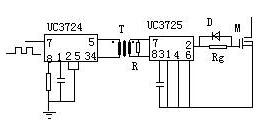

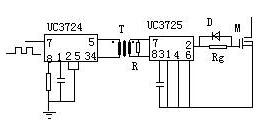

(3)集成芯片UC3724/3725構(gòu)成的驅(qū)動(dòng)電路

電路構(gòu)成如下圖所示。其中UC3724用來(lái)產(chǎn)生高頻載波信號(hào),載波頻率由電容CT和電阻RT決定。一般載波頻率小于600kHz,4腳和6腳兩端產(chǎn)生 高頻調(diào)制波,經(jīng)高頻小磁環(huán)變壓器隔離后送到UC3725芯片7、8兩腳經(jīng)UC3725進(jìn)行調(diào)制后得到驅(qū)動(dòng)信號(hào),UC3725內(nèi)部有一肖特基整流橋同時(shí)將 7、8腳的高頻調(diào)制波整流成一直流電壓供驅(qū)動(dòng)所需功率。一般來(lái)說(shuō)載波頻率越高驅(qū)動(dòng)延時(shí)越小,但太高抗干擾變差;

隔離變壓器磁化電感越大磁化電流越 小,UC3724發(fā)熱越少,但太大使匝數(shù)增多導(dǎo)致寄生參數(shù)影響變大,同樣會(huì)使抗干擾能力降低。根據(jù)實(shí)驗(yàn)數(shù)據(jù)得出:對(duì)于開(kāi)關(guān)頻率小于100kHz的信號(hào)一般 取(400~500)kHz載波頻率較好,變壓器選用較高磁導(dǎo)如5K、7K等高頻環(huán)形磁芯,其原邊磁化電感小于約1毫亨左右為好。

這種驅(qū)動(dòng)電路僅適合于信 號(hào)頻率小于100kHz的場(chǎng)合,因信號(hào)頻率相對(duì)載波頻率太高的話,相對(duì)延時(shí)太多,且所需驅(qū)動(dòng)功率增大,UC3724和UC3725芯片發(fā)熱溫升較高,故 100kHz以上開(kāi)關(guān)頻率僅對(duì)較小極電容的MOSFET才可以。對(duì)于1kVA左右開(kāi)關(guān)頻率小于100kHz的場(chǎng)合,它是一種良好的驅(qū)動(dòng)電路。該電路具有以 下特點(diǎn):?jiǎn)坞娫垂ぷ鳎刂菩盘?hào)與驅(qū)動(dòng)實(shí)現(xiàn)隔離,結(jié)構(gòu)簡(jiǎn)單尺寸較小,尤其適用于占空比變化不確定或信號(hào)頻率也變化的場(chǎng)合。

集成芯片UC3724/UC3725構(gòu)成的驅(qū)動(dòng)電路

烜芯微專業(yè)制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

烜芯微專業(yè)制造二三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點(diǎn)擊右邊的工程師,或者點(diǎn)擊銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹