一、阱構成技術

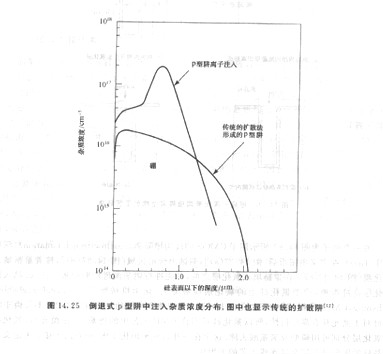

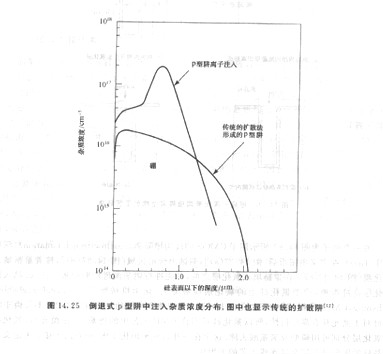

在CMOS中,阱可為單阱(single well)、雙阱(twin well)或是倒退阱(retrograde well).雙阱工藝有一些缺陷,如需高溫工藝(超越1 050℃)及長擴散時間(超越8h)來到達所需2μm~31'm的深度,在這個工藝中,外表的摻雜濃度是最高的,摻雜濃度隨著深度遞加,為了降低工藝溫度和時間,可應用高能量的離子注入將離子直接注入到想要的深度而不需經(jīng)過外表擴散,如此一來,深度由離子注入的能量米決議,因而我們可用不同的注入能景來設計不同深度的阱.在這個工藝中,阱的摻雜散布峰值將位于硅襯底中的某個深度,因此被稱為倒退阱,圖14. 25顯現(xiàn)在倒退阱與普通傳統(tǒng)熱擴散阱中摻雜散布的比擬,關于n型倒退阱與p型倒退阱而言,所需的能嚴分別為700keV及400keV.如前所提,高能離子注入的優(yōu)點在于叮在低溫及短時間的條件下構成阱,故可降低橫向擴散及增加器件密度.倒退阱優(yōu)于傳統(tǒng)阱的中央有:①由于在底部的高摻雜濃度,倒退阱的阻值較傳統(tǒng)阱低,所以能夠?qū)㈤V鎖問題降至最低;②溝道阻斷可與倒退阱的離子注入同時構成,減少工藝步驟與時間;③在底部較高的阱摻雜能夠降低源極與漏極產(chǎn)生穿通(punch-rhrough,或譯貫串、碰透)的幾率.

二、先進隔離技術

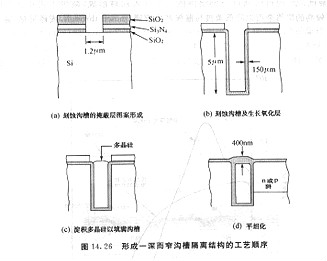

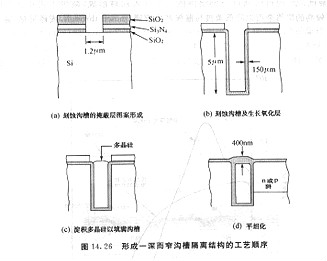

傳統(tǒng)的隔離工藝(14,3,l節(jié))有一些缺陷,使得其不合適用于深亞微米(小于o.25μ.m)工藝,硅的高溫氧化與長氧化時間形成用于溝道阻斷的注入離子(對n-MOSFET而言,通常為硼)侵入有源區(qū)域( active region)并招致VT偏移.因而,橫向氧化會招致有源器件區(qū)域的面積減小,此外,在亞微米隔離的距離中,場氧化層的厚度明顯小于生長在寬距離中的場氧化層,溝槽隔離技術能夠防止這些問題,且已成為隔離的主流技術,圖14. 26顯現(xiàn)構成一深(大于3μm)而窄(小于2μm)的溝槽隔離技術的工藝次第,其包含四個步驟:開出圖形、刻蝕硅襯底、填充介電資料(如二氧化硅或無摻雜的多晶硅)及平整化,深溝槽隔離可用于先進CMOS與雙極型器件及溝槽式DRAM.由于隔離資料是應用CVD淀積,所以不需求長時間或高溫工藝,且能夠消弭橫向氧化和硼侵入( boron encroachment)的問題.

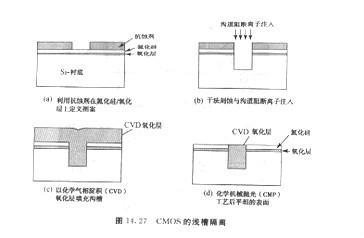

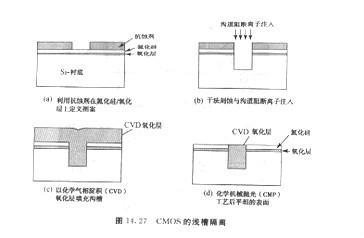

另一個例子為圖14. 27所示用于CMOS的淺溝槽隔離(shallow trench isolation)(深度小于lμm).在定義出圖形后(圖14。27(a),刻蝕出溝槽區(qū)域[圖14. 27(b》,接著重新填入氧化層[圖14.27(C)].在重新填人氧化層之前,可先停止用于溝道阻斷的離子注入,填入的氧化層高過溝槽,位于氮化硅上的氧化層應被除去,化學機械拋光( chemical-mechanicalpolishing,CMP)用來去除位于氮化硅上的氧化層以得到平整的外表[圖14.27(d)].由于氮化硅關于拋光具有高抵御性,所以氮化硅可當作CMP工藝中的掩蔽層,在拋光后,氮化硅和氧化層分別可用磷酸及氫氟酸去除.這個在一開端的平整化步驟,將有助于接下來定義出多晶硅的圖形及多層金屬連線工藝的平整化.

三、柵極工程技術

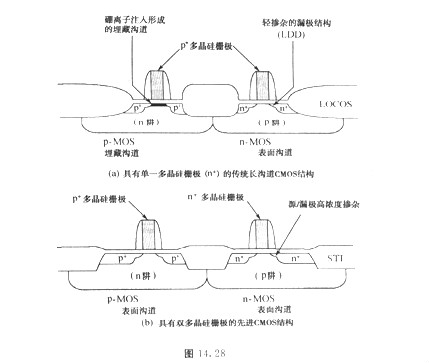

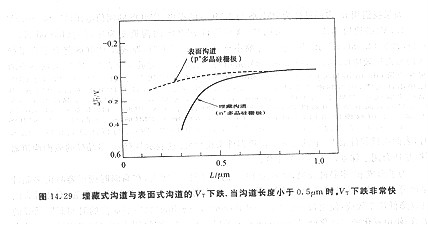

假如我們用n+多晶硅作為PMOS與NMOS的柵極,PMOS的閾值電壓(vTP≈-o.5V~-1.OV)必需用硼離子注入來調(diào)整,這會使得PMOS的溝道變?yōu)槁癫厥?buried chan-nel),如圖14. 28(a)所示,當器件尺寸減少至o.25μm以下時,埋藏式PMOS將會遭遇很嚴重的短溝道效應(short channel effect).最值得留意的是短溝道效應有v,下跌、漏場感應的勢壘降落(drain-induced barrier lowering,DIBL)及在關閉狀態(tài)時大的漏電流,致使于即便柵極電壓為零,也有漏電流經(jīng)過源極與漏極.為處理這個問題,關于PMOS而言,可用p、多晶硅來取代n+多晶硅,由于功函數(shù)(work function)的差別(n+多晶硅與p、多晶硅有1.OeV的差別),外表p型溝道器件并不需求調(diào)整VT的硼離子注入,因而,當技術縮至o.25J'm以下,需求采用雙柵極構造( dual-gate),即p+多晶硅用于PMOS,n+多晶硅用于NMOS[圖14. 28(b》.外表溝道與埋藏溝道的Vl,比擬如圖14. 29所示,能夠留意到在深亞微米時,外表溝道器件的Vr下跌比埋藏溝道器件來得遲緩,這表示具有p+多晶硅的外表溝道器件,很合適用于深亞微米器件的工作,為了構成p’多晶硅柵極,通常用BFz、的離子注入,但是,在高溫時硼很容易由多晶硅穿過薄氧化層抵達硅襯底而形成Vr偏移.此外,氟原子的存在會增加硼的穿透.有幾種辦法能夠降低這個效應:運用快速退火(rapid thermal annealing)以減少高溫的時間而降低硼的擴散,運用氮化的二氧化硅層(nitrided oxide)以抑止硼的穿透(由于硼能夠很容易與氮分離而變得較不易挪動);制造多層的多晶硅,應用層與層間的界面去捕捉硼原子.

烜芯微專業(yè)制造二極管,三極管,MOS管,20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹