電子產(chǎn)品生產(chǎn)革命的一項技術(shù)是“ 集成電路 ”。該技術(shù)通過增加每個芯片的邏輯門密度來減小電子產(chǎn)品的尺寸。今天,我們有不同類型和配置的IC。正如我們在周圍觀察到的那樣,我們發(fā)現(xiàn)有些IC僅可用于一種特定的應(yīng)用,而有些IC可以重新編程并用于各種應(yīng)用。這些類型的IC稱為ASIC。但是它們有何不同?如何對其進行重新編程?為什么有些IC無法重新編程?希望找到這些問題的答案。

什么是ASIC(專用集成電路)?

ASIC的完整形式是“ 專用集成電路”。這些電路是專用的,即為特定應(yīng)用量身定制的IC。這些通常是根據(jù)特定應(yīng)用程序的要求從根級別設(shè)計的。一些特定于應(yīng)用的基本集成電路示例包括玩具中使用的芯片,用于存儲器和微處理器接口的芯片等……這些芯片只能用于設(shè)計了這些芯片的那個應(yīng)用。大概,這些類型的IC僅對那些生產(chǎn)量大的產(chǎn)品是首選。由于ASIC是從根本上設(shè)計的,因此它們具有很高的成本,并且僅建議用于批量生產(chǎn)。

ASIC的主要優(yōu)點是減小了芯片尺寸,因為在單個芯片上構(gòu)造了電路的大量功能單元。現(xiàn)代ASIC通常包括32位微處理器,存儲塊,網(wǎng)絡(luò)電路等。這類ASIC被稱為片上系統(tǒng)。隨著制造技術(shù)的發(fā)展和對設(shè)計方法的研究的不斷發(fā)展,具有不同定制級別的ASIC被開發(fā)出來。

ASIC類型

ASIC是根據(jù)允許程序員在芯片上進行的定制量來分類的。

全定制

在這種類型的設(shè)計中,所有邏輯單元都是為特定應(yīng)用量身定制的,即設(shè)計人員必須專門為電路制造邏輯單元。所有用于互連的掩模層都是定制的。因此程序員無法更改芯片的互連,并且在編程時必須了解電路布局。

完全定制ASIC的最佳示例之一是微處理器。這種類型的定制允許設(shè)計人員在單個IC上構(gòu)建各種模擬電路,優(yōu)化的存儲單元或機械結(jié)構(gòu)。該ASIC成本高昂并且制造和設(shè)計非常耗時。設(shè)計這些IC所需的時間約為八周。

這些通常用于高級應(yīng)用程序。最大的性能,最小的面積和最高的靈活性是完全定制設(shè)計的主要功能。最終,設(shè)計中的風險很高,因為未對邏輯單元,電阻器等使用的電路元件進行預(yù)測試。

半定制

在這種類型的設(shè)計中,邏輯單元是從標準庫中獲取的,即,它們不是像完全定制設(shè)計中那樣手工制作的。有些口罩是定制的,有些則是從預(yù)先設(shè)計的庫中提取的。基于從庫中獲取的邏輯單元的類型以及互連允許的定制量,這些ASIC分為兩種類型:基于標準單元的ASIC和基于門陣列的ASIC。

1)基于標準單元的ASIC

首先要了解這些IC,讓我們了解標準單元庫的含義。某些邏輯單元(例如與門,或門,多路復用器,觸發(fā)器)由設(shè)計人員使用不同的配置進行預(yù)先設(shè)計,并以庫的形式進行標準化和存儲。該集合稱為標準單元庫。

在基于標準單元的標準邏輯庫中,使用了這些標準庫中的ASIC邏輯單元。在ASIC芯片上,標準單元區(qū)域或柔性塊由以行形式排列的標準單元組成。連同這些靈活的模塊,在芯片上使用大型單元,例如微控制器甚至微處理器。這些兆單元也稱為兆功能,系統(tǒng)級宏,固定塊,功能標準塊。

上圖表示具有單個標準單元區(qū)域和四個固定塊的標準單元ASIC。遮罩層是自定義的。設(shè)計人員可以在此處將標準單元放置在管芯上的任何位置。這些也稱為C-BIC。

2)基于門陣列的ASIC

這種類型的半定制ASIC 在硅晶圓上具有預(yù)定義的晶體管,即設(shè)計人員無法更改管芯上存在的晶體管的位置。基本陣列是門陣列的預(yù)定義模式,基本單元是基本陣列中最小的重復單元。

設(shè)計人員僅負責使用管芯的前幾個金屬層來改變晶體管之間的互連。設(shè)計人員從門陣列庫中進行選擇。這些通常稱為“屏蔽門陣列”。基于門陣列的ASIC有三種類型。它們是通道化門陣列,無通道門陣列和結(jié)構(gòu)化門陣列。

a)通道門陣列

在這種類型的門陣列中,在晶體管行之間留有布線空間。這些類似于CBIC,因為在塊之間保留了用于互連的空間,但在通道式門陣列單元行中的高度固定,而在CBIC中,此空間可以調(diào)整。

該門陣列的一些主要特征是-該門陣列使用行之間的預(yù)定義空間進行互連。制造時間為兩天到兩周。

b)無通道門陣列

如通道門陣列中所示,在單元的行之間沒有用于路由的剩余空間。這里的布線是從門陣列單元上方進行的,因為我們可以自定義金屬1和晶體管之間的連接。對于布線,我們不用使用位于布線路徑中的晶體管。生產(chǎn)準備時間約為兩周。

c)結(jié)構(gòu)化門陣列

如上所示,這種類型的門陣列具有嵌入式塊以及門陣列行。結(jié)構(gòu)化門陣列具有較高的CBIC面積效率。像屏蔽門陣列一樣,它們具有較低的成本和更快的周轉(zhuǎn)時間。在此,嵌入式功能的固定大小會限制結(jié)構(gòu)化門陣列。例如,此門陣列是否包含為32k位控制器保留的區(qū)域,但是如果在應(yīng)用程序中我們僅需要16k位控制器的區(qū)域,則剩余區(qū)域?qū)⒈焕速M。所有門陣列的周轉(zhuǎn)時間為兩天到兩周,并且全部都有定制的互連。

專用集成電路(ASIC)設(shè)計流程

逐步設(shè)計ASIC。此步驟順序稱為ASIC設(shè)計流程。下面的流程圖中給出了設(shè)計流程的步驟。

設(shè)計輸入:在此步驟中,使用諸如VHDL,Verilog和System Verilog之類的硬件描述語言來實現(xiàn)設(shè)計的微體系結(jié)構(gòu)。

邏輯綜合:在此步驟中,將使用HDL準備要使用的邏輯單元的網(wǎng)表,互連的類型以及應(yīng)用程序所需的所有其他部件。

系統(tǒng)分區(qū):在這一步,我們將大型裸片劃分為ASIC裸片。

布局前仿真:在此步驟中,進行仿真測試以檢查設(shè)計是否包含任何錯誤。

平面規(guī)劃:在此步驟中,將網(wǎng)表塊安排在芯片上。

放置:在此步驟中,確定塊內(nèi)單元的位置。

路由:在此步驟中,將在塊和單元之間繪制連接。

提取:在此步驟中,我們確定電性能,例如電阻值和互連的電容值。

布局后仿真:在提交用于制造的模型之前,需要完成此仿真,以檢查系統(tǒng)是否正常運行以及互連負載。

ASIC的優(yōu)缺點

ASIC的優(yōu)點如下:

1、 ASIC的小尺寸使其成為復雜的大型系統(tǒng)的理想選擇。

2、由于在單個芯片上構(gòu)建了大量電路,這導致了高速應(yīng)用。

3、 ASIC具有低功耗。

4、 由于它們是芯片上的系統(tǒng),因此電路并排存在。因此,連接? 各種電路所需的布線極少。

5、ASIC沒有時序問題和后期制作配置。

ASIC的缺點如下:

1、 由于這些是定制芯片,因此它們的編程靈活性較低。

2、 由于必須從根本上設(shè)計這些芯片,因此它們的單位成本較高。

3、ASIC擁有更大的上市時間。

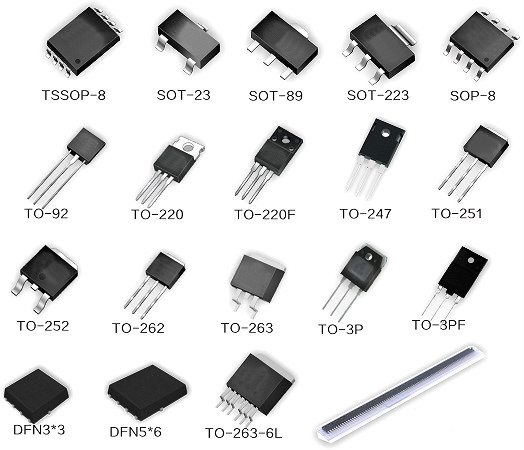

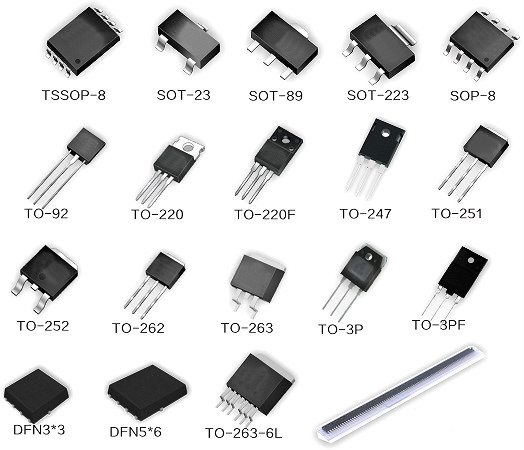

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,1500家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹