CMOS電路中的阱

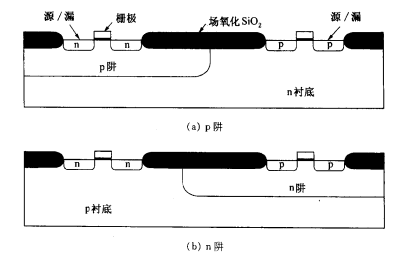

在CMOS電路的工藝結(jié)構(gòu)中,應(yīng)用在襯底上形成反型的阱是一大特點。已有的多種CMOS電路阱的類別,有p阱、n阱、雙阱及倒轉(zhuǎn)阱等(圖4-3-3)。

CMOS電路中的阱-p阱

在a型襯底上,以離子注入摻雜使阱區(qū)域有足夠的濃度,以補償襯底上的n型摻雜并形成一個p阱區(qū)。n型起始材料的摻雜濃度也必須保證能使在其上制備的p溝器件特性符合要求(一般而言,其濃度約3X1014~1X1015 /cm3)。p阱的摻雜濃度也必須高于n型襯底濃度5~10倍。摻雜過濃也將損害n溝器件的性能,例如使遷移率降低,漏源區(qū)結(jié)電容增加,使體效應(yīng)的敏感度增加。

因為p阱CMOS是最早實際制造的CMOS電路所采用的技術(shù),已被工業(yè)界廣泛采用了許多年,因而積累了豐富的經(jīng)驗,是非常成熟的。

采用p阱比n阱有如下幾項優(yōu)點:

(1)在純靜態(tài)邏輯電路中,p阱是一種較好的選擇。在這類電路中兩種型號的MOS器件間的良好平衡是十分有益的。

(2)在某些需要p型隔離區(qū)的場合甚為有利(如需制作npn晶體管等場合)。

(3)由于p阱比n阱具有更少的場反型問題的影響,故更易于制造。

(4)p阱CMOS在SRAM制造中更好,因為用NMOS器件作為貯存單元的增益較高,對于單元信息的讀出和檢測更為有利。

(5)在倒轉(zhuǎn)阱的結(jié)構(gòu)中,摻硼的p阱比摻磷、砷的n阱更為深入襯底,較易形成摻雜離子的倒轉(zhuǎn)分布。

CMOS電路中的阱-n阱

在p型襯底上重摻雜以形成n阱。具有制備p型襯底上NMOS經(jīng)驗的公司,才會將n阱作為CMOS工藝的另一種選擇。本技術(shù)有若干缺點:

(1)比p阱CMOS具有更大的場反型問題,(2)應(yīng)用n阱較難制備純靜態(tài)、高性能的邏輯電路。

CMOS電路中的阱-雙阱

在輕摻雜襯底上,形成兩個隔開的n阱和p阱。襯底可以是輕摻雜的n型或p型材料,或者在一重摻雜襯底上生長輕摻雜外延材料。不論何種襯底材料,其表面的摻雜濃度都大大低于以后將形成的p溝或n溝器件摻雜濃度。

雙阱工藝對亞微米器件具有明顯的優(yōu)點。最重要之點是它有利于制作亞微米溝道,制作對稱的n溝和p溝器件對0.5μm溝道長度以下的器件是有益的。此外,在亞微米尺寸,襯底體摻雜應(yīng)大大提高以克服穿通并維持足夠的閾值電壓。

這樣原來單阱時所帶來的輕摻雜襯底的好處不復存在。雙阱工藝卻可以提供兩種最佳的摻雜分布。另一個好處是:雙阱工藝與外延襯底相結(jié)合,可以靈活地應(yīng)用n+或p+型襯底而不致影響晶體管和電路的性能,也不致改變基本的工藝步驟。

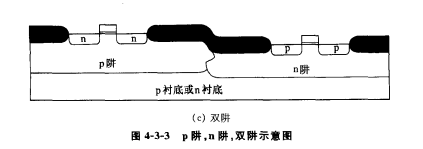

在不同的應(yīng)用場合,需要采用不同型號的襯底和外延層,雙阱工藝顯然是很方便的。最后應(yīng)指出,雙阱工藝較易實現(xiàn)自對準溝道阻止注入,使n溝、p溝管的間距減小。詳細的雙阱剖面圖如圖4-3-4所示。

CMOS電路中的阱-倒轉(zhuǎn)分布阱

普通的單阱或雙阱,均先有離子注入硅片表面,然后在高溫下向體內(nèi)擴散形成。擴散過程既向縱向方向也向橫向方向進行。這當然會影響器件的集成度。

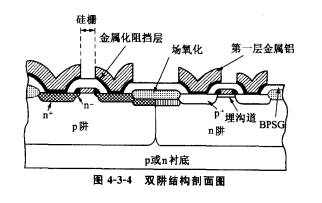

如果將高能離子直接垂直地向si片體內(nèi)注入到一定深度,則無需再進行擴散,必使橫向擴散將大大減少。這樣的離子注入,其摻雜的峰值在硅片內(nèi)一定深度,隨著向表面靠近而衰減,圖4-3-5示出了普通的P阱與倒轉(zhuǎn)阱的B+離子濃度分布圖。用這種方法形成的阱,稱之為倒轉(zhuǎn)分布阱(Retro-grade Well)。

除了能增加集成密度之外,它還具有下列優(yōu)點:

1.對寄生的垂直雙極型晶體管而言,倒轉(zhuǎn)分布阱提供了一種減速場,對于消除CMOS電路中的閂鎖效應(yīng)(Latchup)是有益的。

2.減少垂直的穿通。

3.阱的底部電導率的增加也對保護電路防止閘流效應(yīng)有益。

4.應(yīng)用高能B+離子注入,能夠獲得p阱的高周值電壓的場區(qū)。因為場氧化后,可直接注入B+離子,而先注入B+離子再生長場氧化層,使B+離子分凝到氧化物中去。

倒轉(zhuǎn)分布阱的缺點是結(jié)電容和體效應(yīng)大大增加。當應(yīng)用非常高能量的離子注入形成倒轉(zhuǎn)分布阱時,在漏源區(qū)的底部的摻雜濃度減少,從而減少了漏源區(qū)的結(jié)電容。

在倒轉(zhuǎn)阱中,既有p型的也有n型的。但更廣泛應(yīng)用的是p型倒轉(zhuǎn)阱。因為硼離子的射程較砷、磷離子要大得多,形成n型阱需要用700keV的砷,磷離子注入器,而硼離子注入器只需200~400keV。

在亞微米領(lǐng)域,雙阱和倒轉(zhuǎn)阱應(yīng)用得更為廣泛,當然在工藝過程方面更為復雜,同時增加了成本。

在工藝設(shè)計方面,首先要決定選擇何種阱工藝。隨后,決定隔離的方法,阱的深度,摻雜的分布。阱深將影響到阱之間的距離以及垂直的穿通電壓。摻雜的分布情況將會影響到器件的互導、閾值電壓、漏源間穿通電壓、結(jié)電容、載流子遷移率、漏/源到襯底間的擊穿電壓、體效應(yīng)的靈敏度以及熱載流子效應(yīng)等。

CMOS簡介

CMOS是Complementary Metal Oxide Semiconductor(互補金屬氧化物半導體)的縮寫。它是指制造大規(guī)模集成電路芯片用的一種技術(shù)或用這種技術(shù)制造出來的芯片,是電腦主板上的一塊可讀寫的RAM芯片。因為可讀寫的特性,所以在電腦主板上用來保存BIOS設(shè)置完電腦硬件參數(shù)后的數(shù)據(jù),這個芯片僅僅是用來存放數(shù)據(jù)的。

電壓控制的一種放大器件,是組成CMOS數(shù)字集成電路的基本單元。

而對BIOS中各項參數(shù)的設(shè)定要通過專門的程序。BIOS設(shè)置程序一般都被廠商整合在芯片中,在開機時通過特定的按鍵就可進入BIOS設(shè)置程序,方便地對系統(tǒng)進行設(shè)置。因此BIOS設(shè)置有時也被叫做CMOS設(shè)置。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹