MOS集成電路的功能

(1)放大

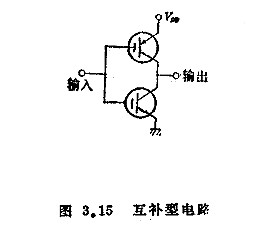

MOS晶體管作為有源元件,本來就是用作放大元件的。在圖3.15所示的互補型電路中,P溝道和N溝道晶體管互為有源元件和負截元件而工作,適用于重負載驅(qū)動和小功率電路。但與單溝道MOS集成電路相比,工藝流程復(fù)雜。

(2)負載

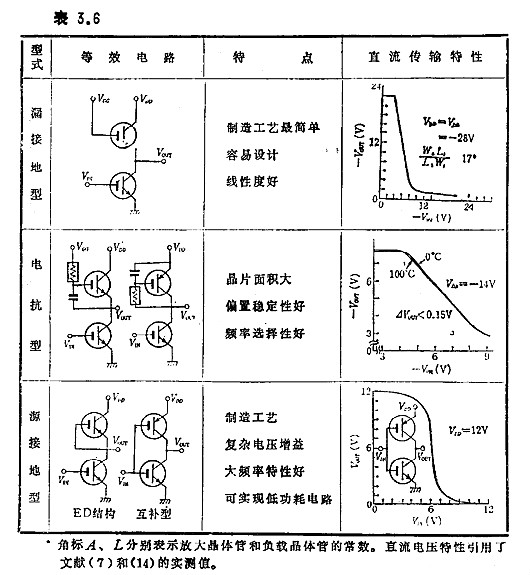

考慮其控制參數(shù)和芯片面積等單項功能,用MOS晶體管做負載要比擴散電阻負載有利。MOS晶體管負載利用了漏-源間的伏安特性,依柵接地的形式大體分為兩種。還加了一種兼具兩者的優(yōu)點的、可實現(xiàn)新功能的電抗型的負載形式。

表中所列的漏接地電路是目前最常用的形式,此時漏與柵均為交流接地。很多場合,為使電路簡單起見,漏和柵接在一起,也就是采用直流連接形式。這種連接多用于增強型負載,由傳輸特性可以看到,輸出電壓的最大值一定在電源電壓扣除V(th)后的差值以下。也就是說電壓利用率很差。

為克服這一缺點,在特殊情形下,Vg用另一電源。另一方面,在源接地型一欄內(nèi)所示的兩種電路,其負載都具有源接地的特性。在E-D結(jié)構(gòu)的電路中,放大晶體管為增強型,負載晶體管為耗盡型。因呈現(xiàn)的是加上V(th)大小的有效柵偏壓的飽和區(qū)特性,故負載接近于恒流負載。從而最大輸出電壓幾乎接近電源電壓,對負載充電的電流也接近于恒流,故具有小功率、高速度的性質(zhì)。

互補型電路,與E-D結(jié)構(gòu)有同樣的效果,但由于負載可以互換,對降低功耗更為有利。也就是說,不管輸入信號為1或0,總有一個晶體管處于截止?fàn)顟B(tài),幾乎沒有電流流過兩個晶體管,只是在1?0轉(zhuǎn)換時,才流過對負載充電的電流。

電抗型電路由漏接地電路和源接地電路組合而成。左側(cè)的電路對直流為漏接地,對交流為源接地。直流傳輸特性就表示了這種情形。若兩個晶體管的尺寸大致相同,傳輸特性可以接近于45°,因而直流穩(wěn)定度可以得到改善,又因為源系交流接地,可以獲得增益。另外還可用于選頻。左側(cè)的圖形為同樣的,電路用互補型構(gòu)成的例子。

(3)傳輸門和模擬開關(guān)

由于對MOS晶體管而言可以對稱地構(gòu)成漏和源,漏和源是雙向開關(guān)的信號端,柵可用作控制端。但在雙極型晶體管中,因有作為控制信號的基極電流流入信號通路,故難以實現(xiàn)雙向功能。但對MOS晶體管而言,雙向開關(guān)可用作下面將要敘述的移位寄存器的傳輸門,存儲器的寫入和讀出門等。又由于漏-源之間沒有偏移電壓,也可用作模擬開關(guān)以及斬波器。

(4)暫存

MOS晶體管的柵輸入電阻極高,由輸入電容和輸入電阻決定的時間常數(shù)通常為幾個毫秒。因此,在輸入端加電壓信號后再切斷信號源時,在毫秒量級的時間內(nèi)還有漏電流流過。可以像在移位寄存器中所用的那樣,用于暫存信息。

(5)非易失性存儲

所謂非易失性存儲是切斷電源后還可保存存儲內(nèi)容的功能。由于半導(dǎo)體單晶沒有撤除外加電壓后的滯后現(xiàn)象,就必須利用不是電路性的而是物理性的存儲現(xiàn)象。我們認為,如用簡單的制造工藝能作成穩(wěn)定的、好用的非易失性存儲器,則半導(dǎo)體存儲器的應(yīng)用領(lǐng)域就會進一步擴大。這方面的研究工作正在進行之中。

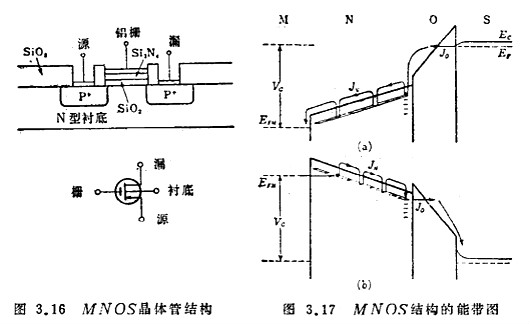

這類存儲器之一種是利用被硅上絕緣膜內(nèi)陷阱所俘獲的電荷來控制硅表面勢。最先做出的非易失性存儲器是MNOS器件,如圖3.16所示。圖3. 17是對該種器件的工作原理的說明。

MNOS是Metal-Silieon Nitride(Si3N4)-Silicon Oxide (SiO2 )- Semiconductor(金屬-氮化硅( Si3N4)一氧化硅(SiO2)-半導(dǎo)體)的縮寫。如圖3.17所示,利用流過Si3N4和SiO2的電流之差,可以改變對Si3N4和SiO2界面處陷阱充電的電荷。

當(dāng)SiO2厚度約為100~50A時,如圖3.17所示,流過SiO2的電流因隧道效應(yīng)通過SiO2勢壘的薄弱部分。當(dāng)SiO2厚度在50A以下時,直接的隧道電流增大。作為這類非易失性存儲器,以后發(fā)表了用AL2O3,做絕緣體的MAS晶體管,和用Al2O3 ~SiO2做絕緣體的MAOS晶體管。

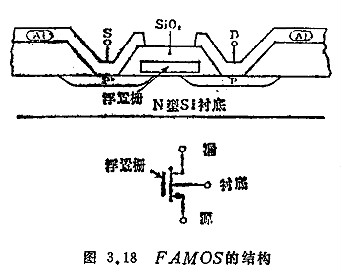

還有一種非易失性存儲器,不是利用電荷穿越絕緣體的隧道現(xiàn)象,而是利用PN結(jié)雪崩擊穿產(chǎn)生的高能電荷越過絕緣體勢壘的現(xiàn)象。圖3.18是利用浮置柵的非易失性存儲器,漏結(jié)雪崩擊穿產(chǎn)生的電子越過SiO2注入到用多晶硅制造的浮置柵內(nèi),電子一經(jīng)注入,就被高度絕緣的SiO2包圍起來,所以能夠長期保存。關(guān)于這種利用雪崩擊穿的方式,還有利用注入電子來寫入,以同樣的方法利用注入空穴消去的電可改寫存儲器。

MOS集成電路的功能

這種存儲器的讀出,在大多數(shù)場合都利用圖3.16、圖3.18所示的MOS晶體管結(jié)構(gòu),通過測量由表面勢變化所產(chǎn)生的源-漏間的電流來進行的。

(1)大規(guī)模MOS集成化的優(yōu)點

與雙極型晶體管相比,MOS晶體管的制造工藝簡單,而且僅用同一種元件就可實現(xiàn)復(fù)雜的功能,所以MOS大規(guī)模集成電路成品率高,有利于大規(guī)模集成化。由于MOS集成電路的阻抗高,可以藉助與源、漏擴散區(qū)同時制作的穿接區(qū),實現(xiàn)立體交叉布線而不影響電路的直流特性。因此,在需要作復(fù)雜布線時,也毋須使用會影響成品率的高難度技術(shù)。

由于阻抗高,為了在分開的集成電路中防止因外部雜散電容而降低工作速度,可以加接緩沖器,但在大規(guī)模集成電路中除了與輸出端相連的單元電路外,毋需接緩沖器,又因為雜散電容小,可以降低單元電路所需的功耗并且能提高速度。

(2)大規(guī)模MOS集成化的功能

進行大規(guī)模集成化時應(yīng)考慮的技術(shù)要點是成品率高、光刻掩模設(shè)計容易、外引線的數(shù)目少等。從掩模設(shè)計和檢驗簡易以及外引線數(shù)目少等方面來看,存儲器和移位寄存器是通過重復(fù)簡單單元電路所構(gòu)成的功能來實現(xiàn)的,因而這方面首先被大規(guī)模集成化。以后又實現(xiàn)了加法器等使用頻度大的器件,現(xiàn)在則可根據(jù)用戶訂貨將任意的一般電路大規(guī)模集成化,集成度可達幾千個元件的規(guī)模。

(3)大規(guī)模MOS集成化的方法

存儲器、移位寄存器等電路沿著盡量減少單元電路面積的方向,經(jīng)過努力實現(xiàn)了大規(guī)模集成化。關(guān)于一般電路的大規(guī)模集成化有如下的方法:在單元電路(門)的周圍設(shè)置供穿接用的擴散區(qū)。

然后根據(jù)不同電路的要求對單元電路進行任意布線的方法;采用縱向擴散區(qū)陣列作為源、漏和穿接區(qū),橫向金屬薄膜陣列作為柵電極和連線,根據(jù)邏輯圖簡單地構(gòu)成大規(guī)模集成電路圖形的方法;將幾種單元電路以變化不大的所有可能圖案的形式存入計算機的程序庫,然后通過計算機將邏輯圖變?yōu)椴季€圖,再由布線圖描繪出大規(guī)模集成電路圖形的自動描圖法。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹