MOS管知識-mosfet體效應(yīng)(襯偏效應(yīng))詳解

mosfet體效應(yīng)(襯偏效應(yīng))詳解

關(guān)于MOSFET的體效應(yīng)(body-effect,襯底調(diào)制效應(yīng)/襯偏效應(yīng)),主要是來源于mos管的S-B(Source-Bulk)端之間的偏壓對MOSFET閾值電壓vth的影響:以NMOS為例,當晶體管的源端(Source)電勢高于體端(Bulk)電勢時,柵下面的表面層中將有更多的空穴被吸引到襯底,使耗盡層中留下的不能移動的負離子增多,耗盡層寬度增加,耗盡層中的體電荷面密度Qdep也增加。

而從一般的MOSFET的閾值電壓的關(guān)系式中Vth與Qdep的關(guān)系(可以考率Vth為MOS柵電容提供電荷以對應(yīng)另一側(cè)耗盡區(qū)固定電荷的大小),可以看到閾值將升高。

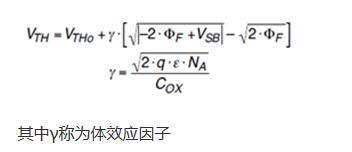

在考慮體效應(yīng)之后,MOS管的閾值電壓可以寫為:

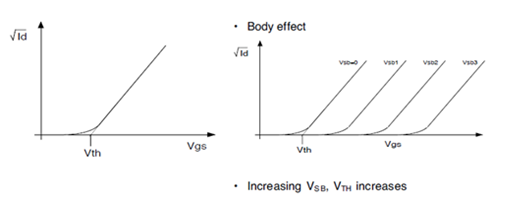

我們亦可以在下圖直觀的了解VSB對Vth的影響:

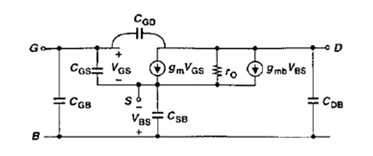

相應(yīng)的,由于體效應(yīng)的存在,在MOSFET的小信號模型中,需要在gm*VGS的電流源旁并聯(lián)一個大小為gmb*VBS的電流源

MOSFET的體效應(yīng)(襯偏效應(yīng))

MOSFET的工作是通過在半導(dǎo)體表面產(chǎn)生導(dǎo)電溝道—表面反型層來進行的,因此器件中存在一個由柵極電壓所誘生出來的p-n結(jié)—場感應(yīng)結(jié)。一旦出現(xiàn)了溝道,則溝道以內(nèi)的耗盡層厚度即達到最大,并保持不再變化(柵電壓不再能夠改變耗盡層厚度)。

(1)什么是襯偏效應(yīng)?

對于MOS-IC而言,在電路工作時,其中各個MOSFET的襯底電位是時刻變化著的,如果對器件襯底的電位不加以控制的話,那么就有可能會出現(xiàn)場感應(yīng)結(jié)以及源-襯底結(jié)正偏的現(xiàn)象;一旦發(fā)生這種現(xiàn)象時,器件和電路即告失效。所以,對于IC中的MOSFET,需要在襯底與源區(qū)之間加上一個適當高的反向電壓——襯偏電壓,以保證器件始終能夠正常工作。簡言之,襯偏電壓就是為了防止MOSFET的場感應(yīng)結(jié)以及源結(jié)和漏結(jié)發(fā)生正偏、而加在源-襯底之間的反向電壓。 由于加上了襯偏電壓的緣故,將要引起若干影響器件性能的現(xiàn)象和問題,這就是襯偏效應(yīng)(襯偏調(diào)制效應(yīng)),又稱為MOSFET的體效應(yīng)。

這種襯偏電壓的作用,實際上就相當于是一個JFET的功能——溝道-襯底的場感應(yīng)p-n結(jié)作為柵極控制著輸出電流IDS的大小。所以,對于加有襯偏電壓的MOSFET,從工作本質(zhì)上來說,可看成是由一個MOSFET和一個JFET并聯(lián)而成的器件,只不過其中JFET的作用在此特別稱為MOSFET的體效應(yīng)而已。這就是說,加上襯偏電壓也就相當于引入了一個額外的JFET。

(2)襯偏效應(yīng)對器件性能的影響: ①MOSFET在出現(xiàn)溝道(反型層)以后,雖然溝道下面的耗盡層厚度達到了最大(這時,柵極電壓即使再增大,耗盡層厚度也不會再增大);但是,襯偏電壓是直接加在源-襯底之間的反向電壓,它可以使場感應(yīng)結(jié)的耗盡層厚度進一步展寬,并引起其中的空間電荷面密度增加,從而導(dǎo)致器件的閾值電壓VT升高。而閾值電壓的升高又將進一步影響到器件的IDS及其整個的性能,例如柵極跨導(dǎo)降低等。 襯底摻雜濃度越高,襯偏電壓所引起的空間電荷面密度的增加就越多,則襯偏效應(yīng)越顯著。例如,p阱-CMOS中的n-MOSFET,它的襯偏效應(yīng)就要比p-MOSFET的嚴重得多。

②由于襯偏電壓將使場感應(yīng)結(jié)的耗盡層厚度展寬、空間電荷面密度增加,所以,當柵極電壓不變時,襯偏電壓就會使溝道中的載流子面電荷密度減小,從而就使得溝道電阻增大,并導(dǎo)致電流減小、跨導(dǎo)降低。 ③當MOSFET在動態(tài)工作時,源極電位是不斷在變化著的,則加在源-襯底之間的襯偏電壓也將相應(yīng)地隨著而不斷變化;這就產(chǎn)生所謂背柵調(diào)制作用,即呈現(xiàn)出一定JFET的功能。 ④由于襯偏電壓會引起背柵調(diào)制作用,使得溝道中的面電荷密度隨著源極電位而發(fā)生變化,即產(chǎn)生了一種電容效應(yīng),這個電容就稱為襯偏電容。襯偏電容的出現(xiàn)即將明顯地影響到器件的開關(guān)速度。

⑤由于MOSFET在加有襯偏電壓時,即將增加一種背柵調(diào)制作用,從而就額外產(chǎn)生出一個與此背柵調(diào)制所對應(yīng)的交流電阻;于是,這就將使得器件的總輸出電阻降低,并導(dǎo)致電壓增益下降。所以,減小襯偏效應(yīng)將有利于提高電壓增益。(3)減弱或消除襯偏效應(yīng)的措施: ①把源極和襯底短接起來,當然可以消除襯偏效應(yīng)的影響,但是這需要電路和器件結(jié)構(gòu)以及制造工藝的支持,并不是在任何情況下都能夠做得到的。

例如,對于p阱CMOS器件,其中的n-MOSFET可以進行源-襯底短接,而其中的p-MOSFET則否;對于n阱CMOS器件,其中的p-MOSFET可以進行源-襯底短接,而其中的n-MOSFET則否。 ②改進電路結(jié)構(gòu)來減弱襯偏效應(yīng)。例如,對于CMOS中的負載管,若采用有源負載來代替之,即可降低襯偏調(diào)制效應(yīng)的影響(因為當襯偏效應(yīng)使負載管的溝道電阻增大時,有源負載即提高負載管的VGS來使得負載管的導(dǎo)電能力增強)。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹