MOS集成電路中的寄生效應(yīng)

在MOS集成電路中,除了電路設(shè)計中需要的MOS管外,還存在著一些不需要的寄生MOS晶體管和電容,它們將給集成電路的正常工作帶來不利的影響,下面將介紹這些MOS集成電路中的寄生效應(yīng)。

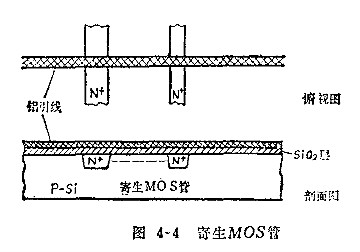

(1)寄生MOS管

MOS集成電路中,當(dāng)電路鋁引線串過兩個擴(kuò)散區(qū)時(例如地鐵式布線),就在這條鋁引線之下形成一個寄生MOS管。如圖4-4所示。

圖中襯底為P型硅,擴(kuò)散區(qū)為N+,當(dāng)鋁引線上加正電壓并當(dāng)正電壓高于開啟電壓時,在兩個N+擴(kuò)散區(qū)之間即形成寄生的N-MOS管。

兩個擴(kuò)散區(qū)本來是兩條不同的電路引線,結(jié)果被寄生MOS管所連通。可見寄生MOS管會給電路帶來不良影響。

為了防止寄生MOS管效應(yīng),在集成電路設(shè)計時,要盡量避免鋁引線橫跨兩個擴(kuò)散區(qū),必不可免時,也要加大擴(kuò)散區(qū)間隔,以減小寄生MOS管的寬長比,增大它的導(dǎo)通電阻。

或者在工藝上增加二氧化硅層的厚度,使得正常運用時寄生MOS管不至導(dǎo)通。

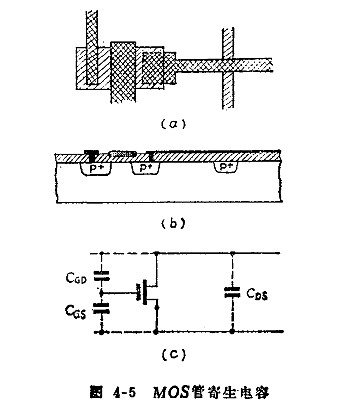

(2)寄生電容

MOS集成電路中的寄生效應(yīng):MOS集成電路中除了MOS管本身具有的MOS電容外,還存在著一些寄生電容,主要寄生電容有Cgs: MOS管柵極與源區(qū)之間寄生電容。Cgd: MOS管柵極與漏區(qū)的寄生電容。

這是由于柵極金屬要交疊覆蓋一部分源漏區(qū)而形成的(參見圖4-5( b)),其數(shù)值大約為0.03PF/μm°。

另一種寄生電容是源漏極之間的Cds。 Cds包括寄生MOS管電容;源漏區(qū)對襯底的PN結(jié)電容和金屬引線與擴(kuò)散區(qū)之間的電容。寄生電容中對MOS管特性影響最大的是柵極與漏極之間的寄生電容Cgd,因為它會對信號起負(fù)反饋作用(參見圖4-5(c))。

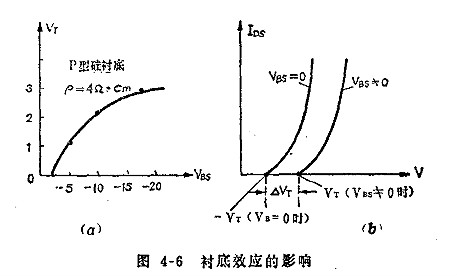

(3)MOS集成電路中的襯底效應(yīng)

MOS集成電路中的寄生效應(yīng):在MOS晶體管中,通常源極是和襯底接在一起的,它們具有相同的電位。

但是,在MOS集成電路中,所有的MOS管都是制作在同一襯底硅片之上的,襯底是公共的。顯然各個MOS管的源極不可能全與襯底相連,否則就會造成部分MOS管的短路,影響構(gòu)成電路。

MOS集成電路中,襯底接在一定電位上( N-MOS襯底接電路中最低電位點,P-MOS襯底接電路中最高電位點),以保證各MOS管之間的“隔離”。

這樣就使得MOS集成電路中某些MOS管的襯底電位與源極電位不再相同了,形成了襯底與源極之間偏壓VBS。

很顯然,VBS是這些MOS管襯底與源極之聞的反向偏壓。故源極與襯底之間的耗盡層比村底與源極相連時要加寬。從而造成MOS管開啟電壓的變化。以N-MOS反相器為例,開啟電壓Vr與襯源偏壓VBS之間關(guān)系如圖4-6所示。

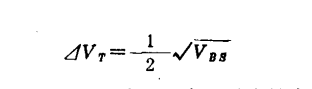

從圖中可以看出,對N-MOS管襯源電壓VBS增加時,開啟電壓Vr也要加大。在電路設(shè)計上VBS對開啟電壓變化量⊿Vr的影響可以用下面近似公式估算:

需要指出:MOS集成電路中存在襯底效應(yīng)并不是一件壞事,恰當(dāng)?shù)乩靡r底效應(yīng)可以制造出增強(qiáng)型MOS管。

因為選用低電阻率(高摻雜)的P型硅片制造N型增強(qiáng)型MOS管會增加各擴(kuò)散區(qū)的勢壘電容,影響電路工作速度,而選用高電阻率的P型硅;

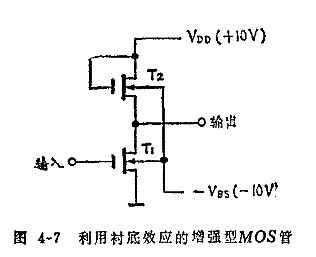

由于工藝上難以使二氧化硅層中的正電荷(例如鈉離子沾污)完全消除,因而很難形成增強(qiáng)型MOS管在MOS集成電路中,襯底不接地電位,而是接在另外一個負(fù)電源上,這樣襯底與管子源極之間就存在著一個負(fù)電壓(如圖4-7所示),使管子獲得一個開啟電壓值,從而得到增強(qiáng)型N-MOS管。

烜芯微專業(yè)制造二極管,三極管,MOS管,橋堆等20年,工廠直銷省20%,4000家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以點擊右邊的工程師,或者點擊銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹