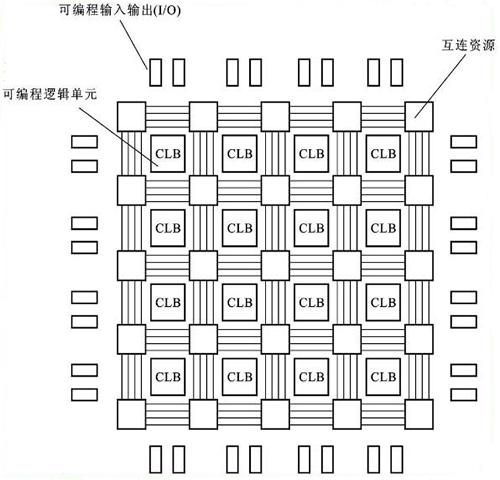

FPGA 器件屬于專用集成電路中的一種半定制電路,是可編程的邏輯列陣,能夠有效的解決原有的器件門電路數(shù)較少的問題。FPGA的基本結(jié)構(gòu)包括可編程輸入/輸出單元,可配置邏輯塊,數(shù)字時(shí)鐘管理模塊,嵌入式塊RAM,布線資源,內(nèi)嵌專用硬核,底層內(nèi)嵌功能單元。每個(gè)單元簡介如下:

FPGA基本結(jié)構(gòu)

1.可編程輸入/輸出單元(I/O單元)

目前大多數(shù)FPGA的I/O單元被設(shè)計(jì)為可編程模式,即通過軟件的靈活配置,可適應(yīng)不同的電器標(biāo)準(zhǔn)與I/O物理特性;可以調(diào)整匹配阻抗特性,上下拉電阻;可以調(diào)整輸出驅(qū)動(dòng)電流的大小等。

2.可編程邏輯單元

FPGA的基本可編程邏輯單元是由查找表(LUT)和寄存器(Register)組成的,查找表完成純組合邏輯功能。FPGA內(nèi)部寄存器可配置為帶同步/異步復(fù)位和置位、時(shí)鐘使能的觸發(fā)器,也可以配置成為鎖存器。FPGA一般依賴寄存器完成同步時(shí)序邏輯設(shè)計(jì)。

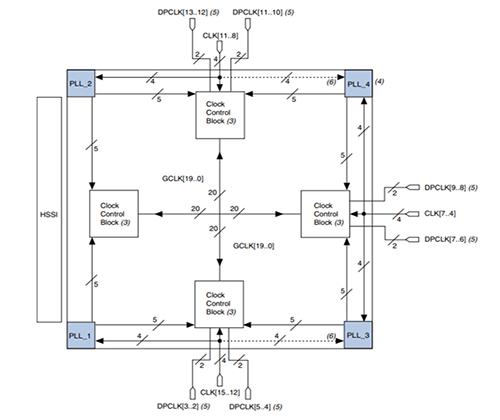

3.時(shí)鐘管理

時(shí)鐘資源部分主要包括全局時(shí)鐘樹和鎖相環(huán)兩部分。

全局時(shí)鐘樹又稱全局時(shí)鐘網(wǎng)絡(luò),負(fù)責(zé)把時(shí)鐘分配到器件內(nèi)部的各個(gè)單元,控制器件內(nèi)部所有資源。鎖相環(huán)則可以完成分頻、倍頻、移項(xiàng)等相關(guān)時(shí)鐘的基本操作。全局時(shí)鐘樹是一種時(shí)鐘網(wǎng)絡(luò)結(jié)構(gòu),可以為FPGA內(nèi)部的所有資源提供時(shí)鐘信號,這些資源包括內(nèi)部的寄存器、內(nèi)部的存儲(chǔ)器、輸入輸出管腳寄存器等。

鎖相環(huán)在FPGA中除了分頻、倍頻操作外,還進(jìn)場用于內(nèi)部時(shí)鐘和外部時(shí)鐘保持沿同步,提供需要的外部時(shí)鐘輸出等。

全局時(shí)鐘樹

4.嵌入式塊RAM

目前大多數(shù)FPGA都有內(nèi)嵌的塊RAM。嵌入式塊RAM可以配置為單端口RAM、雙端口RAM、偽雙端口RAM、CAM、FIFO等存儲(chǔ)結(jié)構(gòu)。

CAM,即為內(nèi)容地址存儲(chǔ)器。寫入CAM的數(shù)據(jù)會(huì)和其內(nèi)部存儲(chǔ)的每一個(gè)數(shù)據(jù)進(jìn)行比較,并返回與端口數(shù)據(jù)相同的所有內(nèi)部數(shù)據(jù)的地址。簡單的說,RAM是一種寫地址,讀數(shù)據(jù)的存儲(chǔ)單元;CAM與RAM恰恰相反。

除了塊RAM,Xilinx和Lattice的FPGA還可以靈活地將LUT配置成RAM、ROM、FIFO等存儲(chǔ)結(jié)構(gòu)。

5.布線資源

布線資源連通FPGA內(nèi)部所有單元,連線的長度和工藝決定著信號在連線上的驅(qū)動(dòng)能力和傳輸速度。布線資源的劃分:

(1)全局性的專用布線資源:以完成器件內(nèi)部的全局時(shí)鐘和全局復(fù)位/置位的布線;

(2)長線資源:用以完成器件Bank間的一些高速信號和一些第二全局時(shí)鐘信號的布線。

(3)短線資源:用來完成基本邏輯單元間的邏輯互連與布線;

(4)其他:在邏輯單元內(nèi)部還有著各種布線資源和專用時(shí)鐘、復(fù)位等控制信號線。

由于在設(shè)計(jì)過程中,往往由布局布線器自動(dòng)根據(jù)輸入的邏輯網(wǎng)表的拓?fù)浣Y(jié)構(gòu)和約束條件選擇可用的布線資源連通所用的底層單元模塊,所以常常忽略布線資源。其實(shí)布線資源的優(yōu)化與使用和實(shí)現(xiàn)結(jié)果有直接關(guān)系。

6.底層嵌入功能單元

底層嵌入功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP和CPU等軟處理核(Soft Core)。

7.內(nèi)嵌專用硬核

內(nèi)嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA處理能力強(qiáng)大的硬核(Hard Core),等效于ASIC電路。為了提高FPGA性能,芯片生產(chǎn)商在芯片內(nèi)部集成了一些專用的硬核。

以上就是FPGA的基本結(jié)構(gòu)介紹了。由于FPGA具有布線資源豐富,可重復(fù)編程和集成度高,投資較低的特點(diǎn),在數(shù)字電路設(shè)計(jì)領(lǐng)域得到了廣泛的應(yīng)用。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹