MOS管的GIDL效應是指在柵極電壓較高的情況下,絕緣層下的溝道區(qū)域會發(fā)生漏電現象的現象。這種現象是由于高電場導致絕緣層中的電子發(fā)生穿隧效應,從而形成漏電流。

GIDL效應會導致器件的功耗增加、性能下降,并可能引起電流漂移現象。針對GIDL效應的影響和問題,研究人員提出了一些解決方案,包括使用高介電常數的材料來減小電場強度、優(yōu)化溝道結構和引入電場屏蔽層等方法。此外,還有其他一些方法可以應對GIDL效應,例如采用低功耗工藝、優(yōu)化柵極結構和控制柵極電壓等。

GIDL(gate-induced drain leakage) 是指柵誘導漏極泄漏電流,對MOSFET的可靠性影響較大。

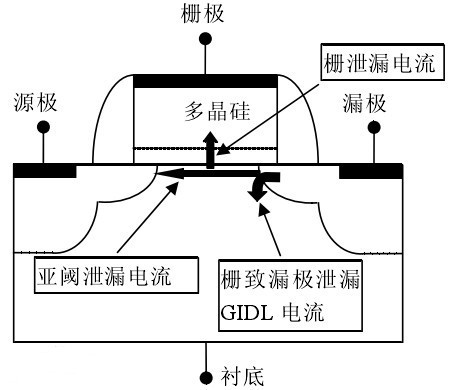

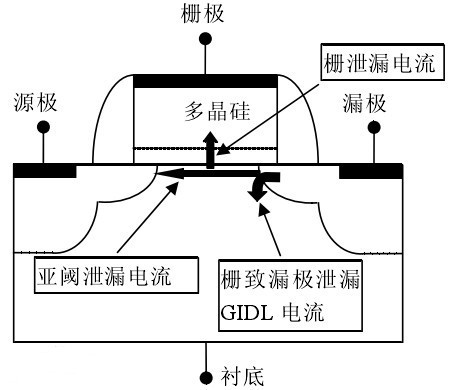

MOSFET 中引發(fā)靜態(tài)功耗的泄漏電流主要有:源到漏的亞閾泄漏電流,柵泄漏電流,發(fā)生在柵漏交疊區(qū)的柵致漏極泄漏 GIDL 電流,如圖所示。在這些泄漏電流中,在電路中器件處于關態(tài)或者處于等待狀態(tài)時,GIDL 電流在泄漏電流中占主導地位。

GIDL 隧穿電流

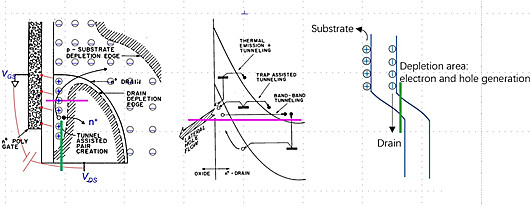

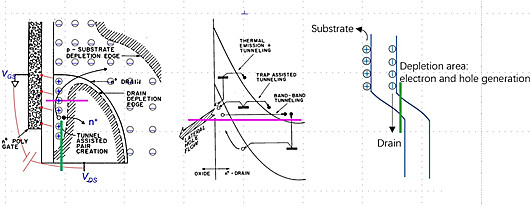

當柵漏交疊區(qū)處柵漏電壓 VDG很大時,交疊區(qū)界面附近硅中電子在價帶和導帶之間發(fā)生帶帶隧穿形成電流,我們把這種電流稱之為 GIDL 隧穿電流。隨著柵氧化層越來越薄,GIDL 隧穿電流急劇增加。

GIDL 產生電流

漏 pn 結由于反偏,產生率大于復合率,在柵控制下,硅和二氧化硅界面處陷阱充當產生中心而引發(fā)的一種柵誘導的漏極泄漏電流。

柵致漏極泄露電流,gate induced drain leakage (GIDL,/GIDL)

柵致漏極泄露電流是由MOS晶體管漏極結中的高場效應引起的。由于G與D重疊區(qū)域之間存在大電場而發(fā)生隧穿并產生電子-空穴對,其中包含雪崩隧穿和BTBT隧穿。由于電子被掃入阱中,空穴積累在漏中形成/GIDL。

以NMOS為例,當gate不加壓或加負壓,drain端加高電壓, 使得gate和drain的交疊區(qū)域出現了一個從drain指向gate的強電場,靠近gate oxide 附近出現強耗盡區(qū),形成電勢變化非常陡的類p+-n+結—橫向和縱向的圖;(一定是gate與drain要有重疊嗎?要有交疊,這也是GIDL管的來源),引起了耗盡區(qū)電子空穴分離,載流子躍遷,電子流向drain端,空穴被掃入基底,由此形成漏電流。

NMOS 中 GIDL 圖解 (橫向、縱向)

前提條件:

1) 亞閾值區(qū)

2)Drain和gate有交疊,GIDL產生處有pn結

3)強漏電場

Impact in MOS:亞域區(qū)漏電流,增大靜態(tài)功耗

Mitigation in MOS: LDD, 交疊區(qū)輕摻雜,使電勢緩變,躍遷幾率減小,漏電流減小

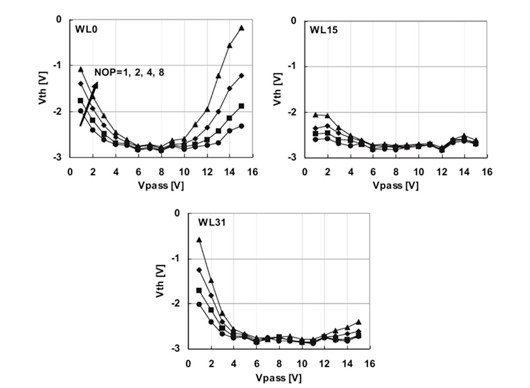

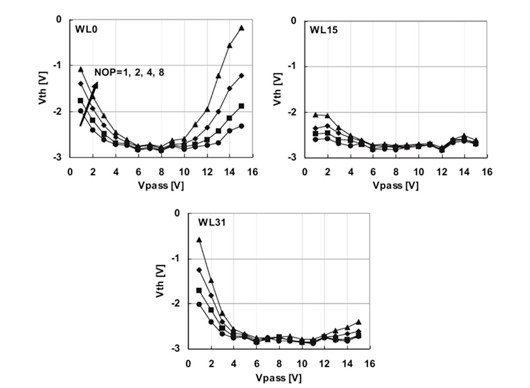

Impact in NAND:在program時,被inhibit string 發(fā)生HCI效應, 邊緣WL Vt上浮 (不被inhibit的string, 不存在靜電壓差,這種效應應該較弱)

Mitigation in MOS: 設置邊緣dummy WL

Application in NAND:GIDL erase,3D NAND中, Pwell erase 需結合SEG工藝,工藝復雜,因此越來越多的制造商開始使用GIDL erase,即利用GIDL效應產生電子空穴對,將空穴掃入channel中,實現塊擦除。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯系下方的聯系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯系號碼:18923864027(同微信)

QQ:709211280