體效應(yīng)詳解

在許多應(yīng)用中,源極直接連接到底物(體極)B極,使得底物和溝道之間的pn結(jié)是零電壓偏置。此時(shí)底物在電路中不發(fā)揮任何作用,可以被忽略。

在集成電路中,底物通常被大量的MOS所共用。為了保證底物和所有溝道之間的pn結(jié)都是截止?fàn)顟B(tài),底物在NMOS中通常被連接到最小負(fù)電壓源(在PMOS中連接到最大正電壓源)。在這種情況下,反向偏置的pn結(jié)會(huì)對(duì)元器件造成影響。為了說(shuō)明這一點(diǎn),考慮一個(gè)NMOS并且讓它的底物電壓比源極電壓低(此時(shí)pn結(jié)反向偏置)。反向偏置的電壓將會(huì)擴(kuò)大耗散區(qū)的體積,這回加深溝道的深度,這會(huì)導(dǎo)致iD增大,為了使得MOS回到原來(lái)的狀態(tài)上,就必須增大 vGS 。

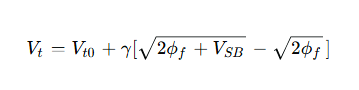

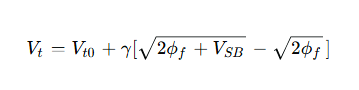

電壓VSB可以看做是改變了閾值電壓Vt,關(guān)系由下面的表達(dá)式給出:

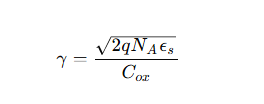

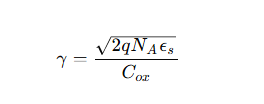

在這里Vt0是在VSB= 0條件下的閾值電壓,?f是一個(gè)物理參數(shù)一般情況是0.6V,γ是制作工藝參數(shù),由下面的表達(dá)式給出:

在這里 q是電子電荷量,NA是p類(lèi)型底物的摻雜濃度,?s是硅的介電常數(shù)。

上式反應(yīng)了增大VSB會(huì)導(dǎo)致 Vt的增加,盡管VGS保持恒定的情況下也會(huì)增大ID 。換句話(huà)說(shuō),VBS同樣能控制ID的大小,因此體極和柵極具有相同的控制ID的能力,這個(gè)效應(yīng)稱(chēng)為體效應(yīng) 。這里 γ 稱(chēng)為體效應(yīng)參數(shù)。

MOS管體效應(yīng)襯偏效應(yīng)

當(dāng)MOS管源端電勢(shì)大于襯底電勢(shì)(VS>VB )時(shí),柵下面的表面層中將有更多的空穴被吸收到襯底上,留下更多不能移動(dòng)的負(fù)離子(負(fù)電中心),使得耗盡層展寬。閾值電壓升高。

1.為什么需要源端電勢(shì)大于襯底電勢(shì)?

因?yàn)閷?duì)于CMOS芯片來(lái)說(shuō),特別是數(shù)字芯片來(lái)說(shuō),其襯底電壓會(huì)存在一定的波動(dòng),如果不對(duì)襯底電壓進(jìn)行限制,則可能出現(xiàn)襯底電壓大于源端電壓的情況,使得PN結(jié)正偏。MOS管失效,所以需要在襯底與源之間加上適當(dāng)?shù)姆雌妷海员WCMOS的工作狀態(tài)。這個(gè)電壓也時(shí)常被稱(chēng)為襯偏電壓。

2.體效應(yīng)有什么影響?

1、耗盡層展寬使得閾值電壓VT升高,進(jìn)而影響器件的GM和IDS等性能。因?yàn)檫@些器件性能均與VT相關(guān)。

2、襯底摻雜濃度越高,襯偏效應(yīng)就越明顯,以典型的CMOS工藝為例,PMOS的襯偏效應(yīng)會(huì)大于普通NMOS的襯偏效應(yīng),因?yàn)橹谱鱌MOS的n阱摻雜大于襯底摻雜(摻雜濃度越高,耗盡層越窄,耗盡層電容越大,使得n阱與襯底隔離),能夠單獨(dú)控制電壓。

3、當(dāng)芯片工作時(shí),MOS管源極的電壓會(huì)不斷的變化,使得源襯之間的電壓也在不斷變化。這就是背柵調(diào)制效應(yīng),即出現(xiàn)了JFET的功能。

4、背柵調(diào)制作用使得溝道中的面電荷密度也隨著源端電壓的變化不斷變化,出現(xiàn)了電容效應(yīng)。稱(chēng)為襯偏電容,該電容會(huì)明顯影響器件的開(kāi)關(guān)速度。

5、背柵調(diào)制效應(yīng)作用對(duì)應(yīng)會(huì)產(chǎn)生一個(gè)交流電阻。該電阻會(huì)使的MOS管的輸出電阻降低,電壓增益下降。

在設(shè)計(jì)中如何降低體效應(yīng)的影響?

1、將源端與漏端短接。這也是采用的方法,如將NMOS的源漏都接地,將PMOS的源漏都接VDD。

2、改進(jìn)電路結(jié)構(gòu)。對(duì)于某些不能將源漏短接的情況,便只能在電路結(jié)構(gòu)層面上進(jìn)行改進(jìn)。如在CMOS中采用有源負(fù)載。

〈烜芯微/XXW〉專(zhuān)業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠(chǎng)直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專(zhuān)業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280