換電路中,發(fā)生在漏極和源極之間的浪涌。

漏極和源極之間產(chǎn)生的浪涌

緩沖電路的種類和選擇

C緩沖電路的設計

RC緩沖電路的設計

放電型RCD緩沖電路的設計

非放電型RCD緩沖電路的設計

封裝引起的浪涌差異

SiC MOSFET的漏極和源極之間產(chǎn)生的浪涌

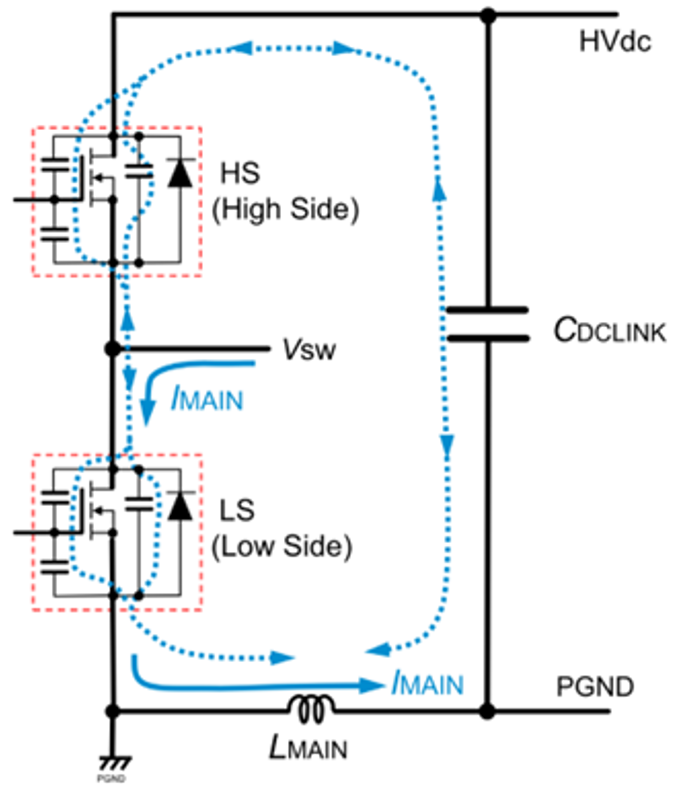

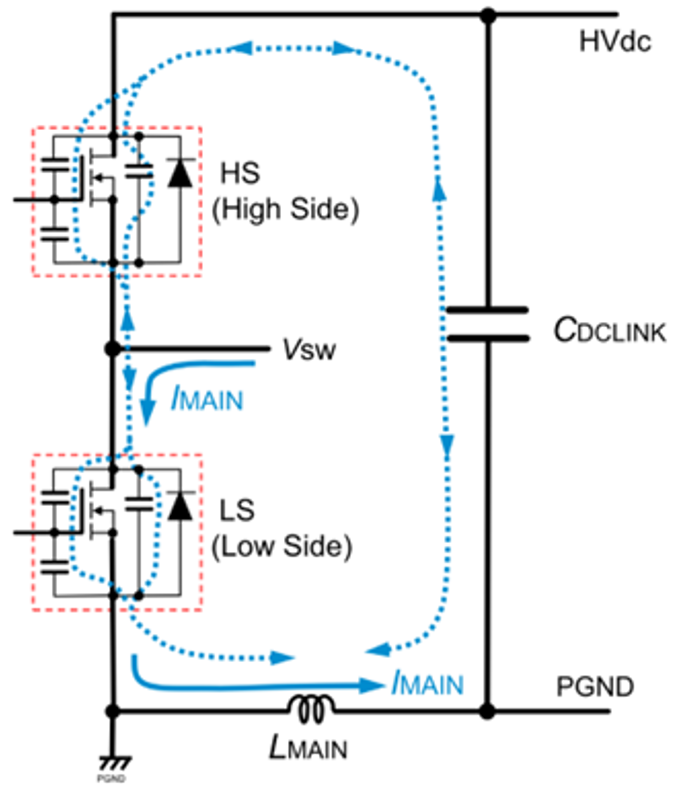

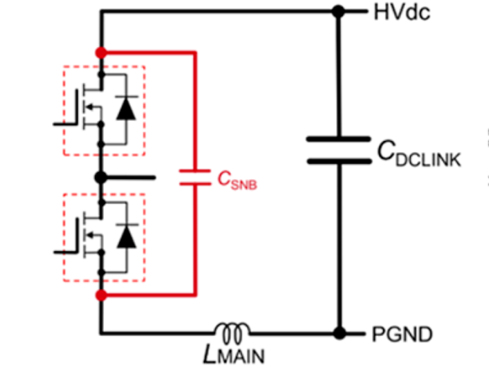

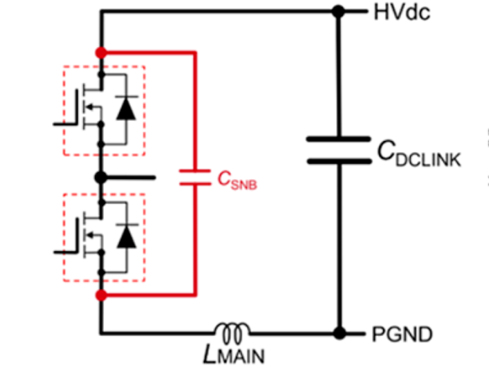

開關導通時,線路和電路板版圖的電感之中會直接積蓄電能(電流能量)。當該能量與開關器件的寄生電容發(fā)生諧振時,就會在漏極和源極之間產(chǎn)生浪涌。下面將利用圖1來說明發(fā)生浪涌時的振鈴電流的路徑。這是一個橋式結構,在High Side(以下簡稱HS)和Low Side(以下簡稱LS)之間連接了一個開關器件,該圖是LS導通,電路中存在開關電流IMAIN的情形。通常,該IMAIN從VSW流入,通過線路電感LMAIN流動。

圖1:產(chǎn)生關斷浪涌時的振鈴電流路徑

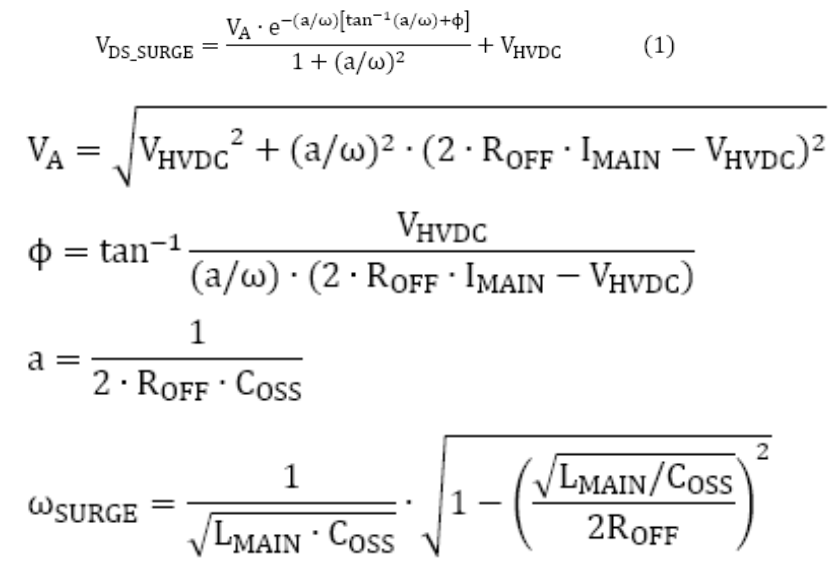

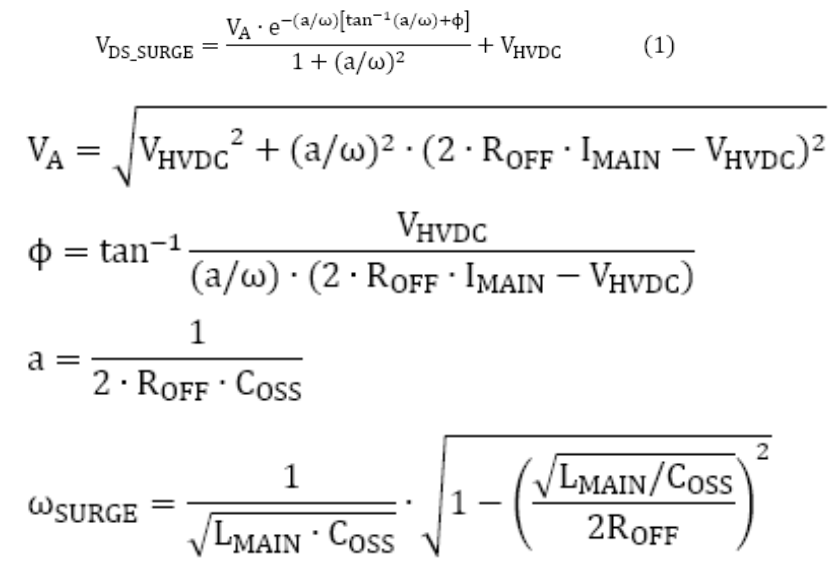

接下來,LS關斷時,流向LMAIN的IMAIN一般是通過連在輸入電源HVdc和PGND之間的大容量電容CDCLINK,經(jīng)由HS和LS的寄生電容,按照虛線所示路徑流動。此時,在LS的漏極和源極之間,LMAIN和SiC MOSFET的寄生電容COSS(CDS+CDG)就會產(chǎn)生諧振現(xiàn)象,漏極和源極之間就會產(chǎn)生浪涌。如果用VDS_SURGE表示施加在HVdc引腳的電壓,用ROFF表示MOSFET關斷時的電阻,則該浪涌的最大值VHVDC可以用下述公式表示(*1)。

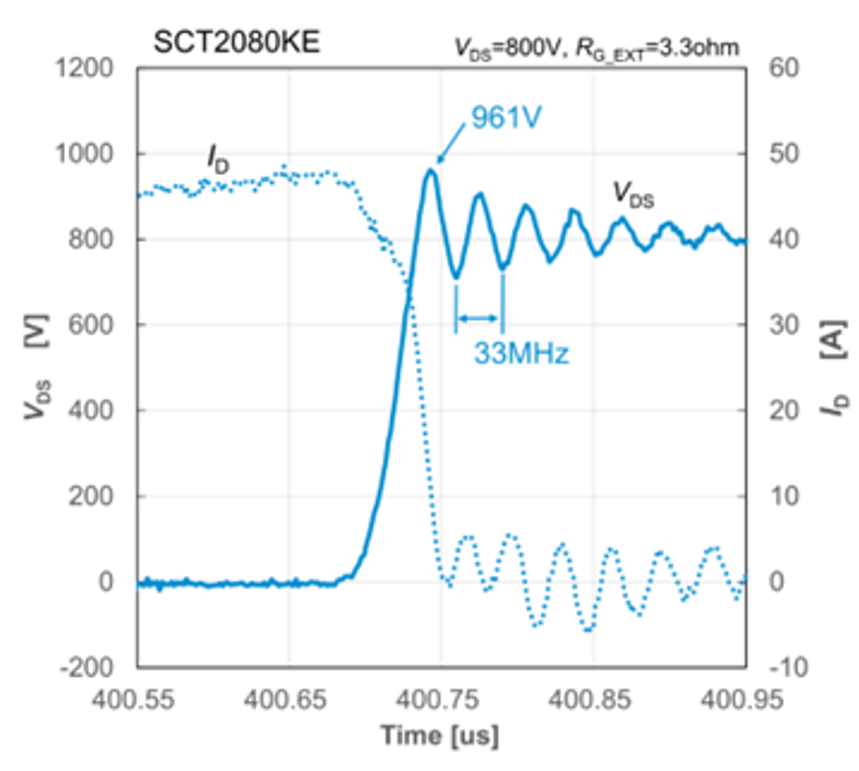

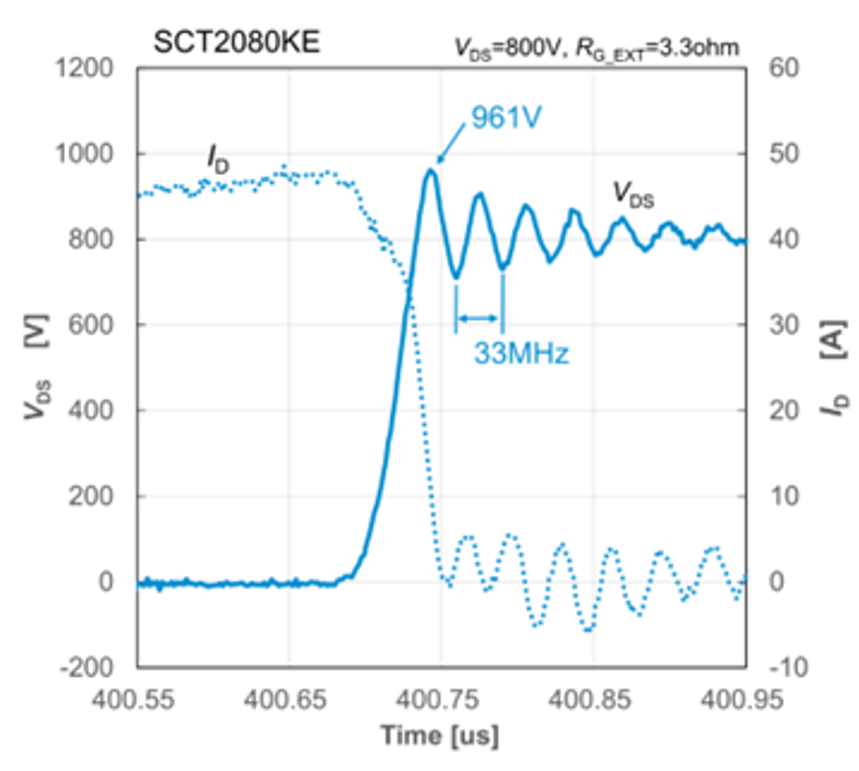

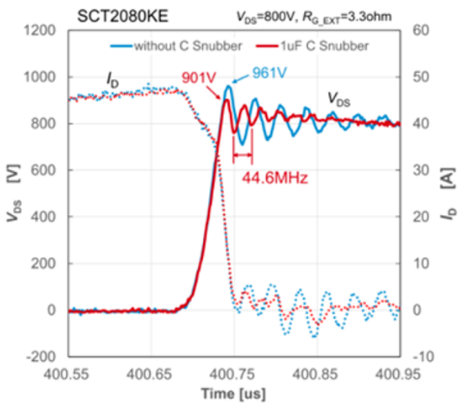

圖2是使用SiC MOSFET SCT2080KE進行測試時關斷時的浪涌波形。當給HVdc施加800V的電壓時,可以算出VDS_SURGE為961V,振鈴頻率約為33MHz。利用公式(1),根據(jù)該波形,可以算出LMAIN約為110nH。

圖2:關斷浪涌波形

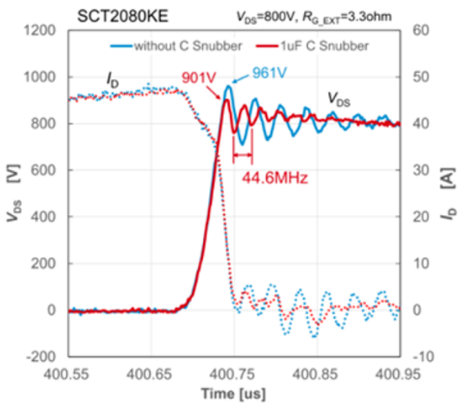

再接下來,增加一個圖3所示的緩沖電路CSNB,實質性地去掉LMAIN后,其關斷浪涌的波形如圖4所示。

圖3:C緩沖電路

圖4:通過C緩沖電路降低關斷浪涌

可以看到,增加該CSNB之后,浪涌電壓降低50V以上(約901V),振鈴頻率也變得更高,達到44.6MHz,而且包括CSNB在內,整個電路中的LMAIN變得更小。

同樣,利用公式(1)計算LMAIN,其結果由原來的110nH左右降低至71nH左右。原本,最好是在進行版圖設計時,將線路電感控制在最低水平。但是,在實際設計過程中,往往會優(yōu)先考慮器件的散熱設計,所以線路并不一定能夠按照理想進行設計。

在這種情況下,其對策方案之一就是盡可能在開關器件附近配置緩沖電路,使之形成旁路電路。這樣既可以將線路電感這一引發(fā)浪涌的根源降至最低,還可以吸收已經(jīng)降至最低的線路電感中積蓄的能量。然后,通過對開關器件的電壓進行鉗制,就可以降低關斷浪涌。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280