作為通道技術(shù)和網(wǎng)絡(luò)技術(shù)結(jié)合的產(chǎn)物,光纖通道(fibre channel)是一種具有高實(shí)時(shí)性、高可靠性、高帶寬,高性價(jià)比的開放式網(wǎng)絡(luò)。任何需要接入到光纖通道網(wǎng)絡(luò)的設(shè)備都需要相應(yīng)的網(wǎng)絡(luò)接口卡(NAC),而網(wǎng)絡(luò)接口卡的核心是接口控制芯片。由于光纖通道標(biāo)準(zhǔn)是一項(xiàng)十分龐大而復(fù)雜的協(xié)議,不同的特性適用于不同的應(yīng)用環(huán)境;又因?yàn)楣饫w通道標(biāo)準(zhǔn)目前仍處于發(fā)展階段,標(biāo)準(zhǔn)的內(nèi)容還在做不停的變化,因此選用FPGA作為當(dāng)前接口控制芯片的載體是一個(gè)非常合適的選擇。一方面對(duì)于不同的應(yīng)用環(huán)境,可以對(duì)相應(yīng)的功能模塊進(jìn)行適當(dāng)?shù)牟脺p,既能滿足應(yīng)用需要又能降低成本;另一方面對(duì)于協(xié)議的變化,基于FPGA的實(shí)現(xiàn)也很容易就能對(duì)老版本設(shè)計(jì)進(jìn)行更新。

1.協(xié)議分析

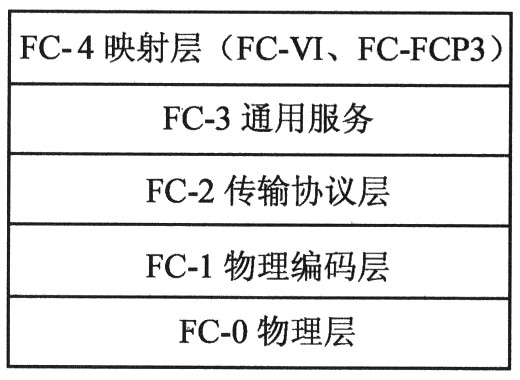

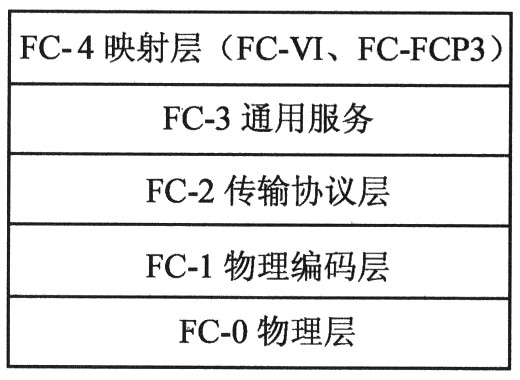

和OSI參考模型類似,光纖通道協(xié)議簇也是以分層的方式來組織各個(gè)協(xié)議的。其分層模型如圖1所示。

圖1 光纖通道分層模型

作為數(shù)據(jù)傳輸協(xié)議,光纖通道支持許多上層協(xié)議,包括VIA、SCSI、IPv4、IPv6、SBCCS、ASM等。在為這些協(xié)議傳輸數(shù)據(jù)之前,需要先將待發(fā)送的數(shù)據(jù)映射成規(guī)定的格式,F(xiàn)C-4層實(shí)現(xiàn)這一映射,對(duì)于每一個(gè)支持的上層協(xié)議,都有一個(gè)映射協(xié)議與之相對(duì)應(yīng)。

FC-3層是一個(gè)通用服務(wù)層,為映射層協(xié)議提供一系列通用服務(wù)。比較重要的幾個(gè)服務(wù)包括:交換注冊(cè)、端口注冊(cè)和注銷服務(wù)。

FC-2層是光纖通道協(xié)議中最重要的一層,定義了將數(shù)據(jù)塊進(jìn)行端到端傳輸?shù)囊?guī)則和機(jī)制,包括不同類型的服務(wù)、幀格式定義、序列的分片和重裝、交換管理、地址分配和多播管理等。

FC-1層定義了串行編碼和解碼規(guī)范,規(guī)定使用8B/10B編碼。

FC-0層是光纖通道協(xié)議的物理層規(guī)范,定義了發(fā)射機(jī)、接收機(jī)、傳輸介質(zhì)以及它們之間的接口規(guī)范。傳輸速率也在這里定義。

2.設(shè)計(jì)方案

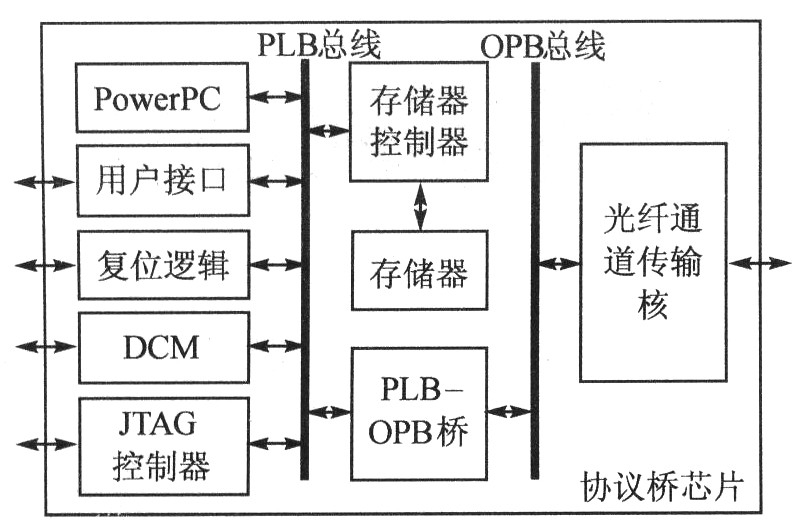

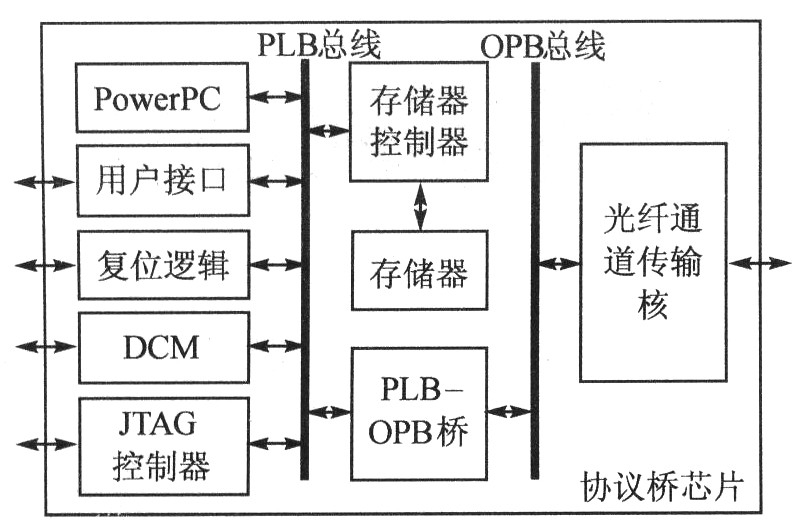

通過對(duì)協(xié)議的分析得出,映射層協(xié)議和具體應(yīng)用環(huán)境密切相關(guān),應(yīng)該由用戶自己實(shí)現(xiàn)。接口控制芯片在邏輯上可以分成三部分,即通用服務(wù)模塊、端到端IU傳輸和緩沖到緩沖幀傳輸;在實(shí)現(xiàn)方式上又可以分為軟件部分和硬件部分。接口控制芯片系統(tǒng)框圖如圖2所示。

圖2 接口控制芯片系統(tǒng)組成

圖2左邊的PowerPC和存儲(chǔ)器控制器通過PLB總線互聯(lián)在一起,構(gòu)建了Linux操作系統(tǒng)和接口控制芯片的軟件部分的運(yùn)行平臺(tái)。

PowerPC架構(gòu)中還包含了通用的OPB總線,用來進(jìn)行外部設(shè)備的互聯(lián)。OPB總線通過一個(gè)PLB-OPB橋連接到PLB總線,如圖2右邊所示。連接到OPB總線的外部設(shè)備只有一個(gè),也就是光纖通道傳輸核。

用戶接口定義了接口控制芯片的用戶接口。根據(jù)應(yīng)用環(huán)境的不同,這個(gè)模塊有不同的實(shí)現(xiàn)方法,如PCI或USB。

當(dāng)用戶有數(shù)據(jù)需要發(fā)送時(shí),通過接口控制芯片的用戶接口將數(shù)據(jù)按標(biāo)準(zhǔn)格式存人芯片內(nèi)部的數(shù)據(jù)存儲(chǔ)器,并通過設(shè)置相應(yīng)的寄存器請(qǐng)求接口控制芯片的數(shù)據(jù)傳輸服務(wù)。然后,軟件代碼將數(shù)據(jù)接管過來,先為這次數(shù)據(jù)(IU)傳輸分配相應(yīng)的軟件資源(交換狀態(tài)塊、序列狀態(tài)塊等)用以記錄數(shù)據(jù)的發(fā)送狀態(tài)。等完成相應(yīng)的處理后,PowerPC通過光纖通道傳輸核提供的接口通知傳輸核對(duì)數(shù)據(jù)進(jìn)行處理,包括分片、成幀、CRC計(jì)算和8B/10B編碼等任務(wù)。最后,傳輸核通過輸出引腳輸出高速串行數(shù)據(jù)去調(diào)制光發(fā)射機(jī)并發(fā)送到光纖鏈路。

當(dāng)從輸入鏈路上接收到數(shù)據(jù)時(shí),傳輸核首先對(duì)數(shù)據(jù)進(jìn)行處理,包括位同步、串并轉(zhuǎn)換、8B/10B解碼、字同步、有序集檢測(cè)、CRC校驗(yàn)和幀提取。當(dāng)有效幀接收到并存到接收緩沖區(qū)后,硬件模塊設(shè)置相應(yīng)的寄存器通知Power-PC,然后PowerPC對(duì)接收到的幀進(jìn)行處理,包括分配相應(yīng)的軟件資源、幀重裝。當(dāng)屬于一個(gè)序列的所有幀都正確接收完后,PowerPC通過用戶接口模塊通知用戶模塊,用戶模塊接收到數(shù)據(jù)后自行進(jìn)行處理。

3.硬件設(shè)計(jì)

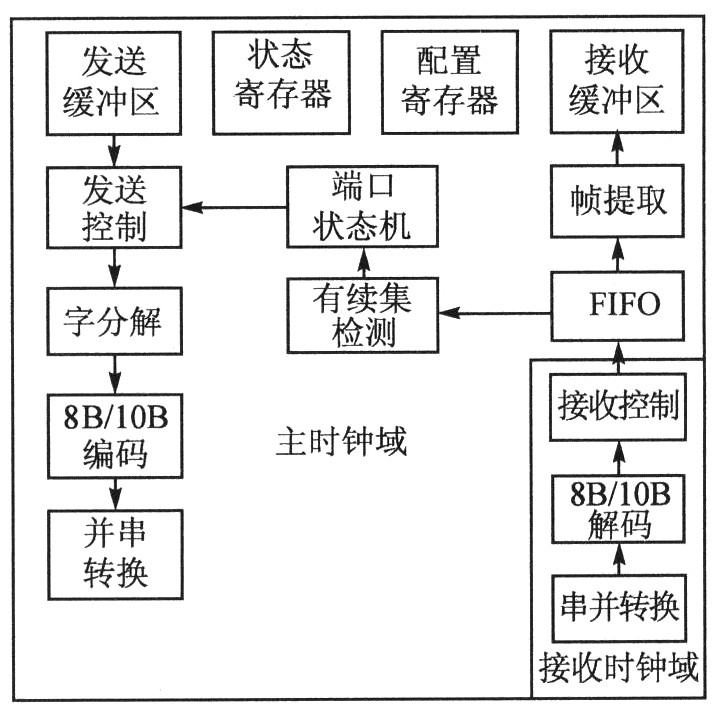

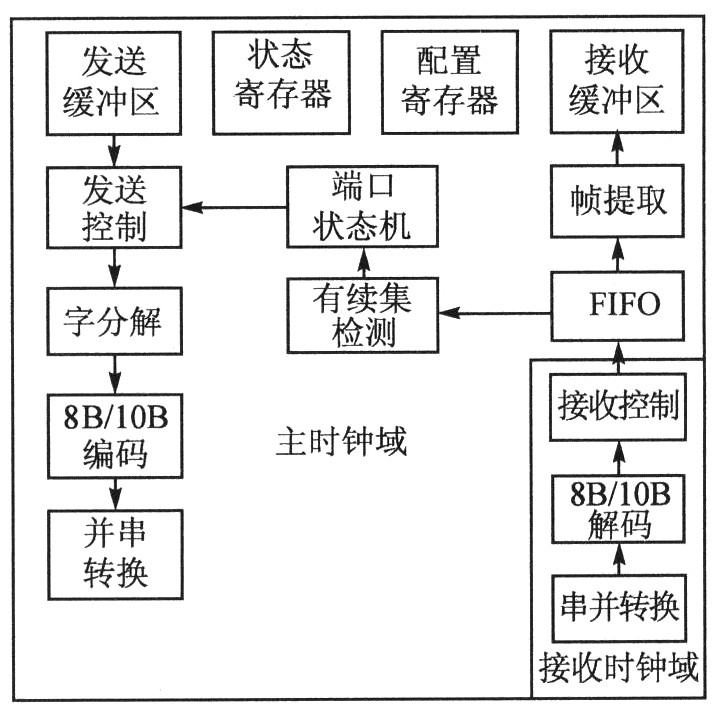

接口控制芯片的硬件部分也就是圖2中的光纖通道傳輸核,負(fù)責(zé)將數(shù)據(jù)幀按標(biāo)準(zhǔn)規(guī)定的格式從發(fā)送緩沖區(qū)傳輸?shù)芥溌妨硪欢说慕邮站彌_區(qū)。為了正確有效地完成這個(gè)任務(wù),接口控制芯片的硬件部分實(shí)現(xiàn)以下一些功能:緩沖到緩沖的流量控制、鏈路級(jí)別的差錯(cuò)檢測(cè)和恢復(fù)、字同步、有序集檢測(cè)、幀提取、8B/10B編解碼和串并/并串轉(zhuǎn)換等功能。接口控制芯片的硬件部分功能框圖如圖3所示。

圖3 光纖通道傳輸核

3.1發(fā)送控制邏輯

發(fā)送控制邏輯的功能是控制幀、原語信號(hào)和原語序列的發(fā)送順序,使之符合光纖通道標(biāo)準(zhǔn),主要包括保證連續(xù)幀之間具有足夠的間隔和在幀之間插入原語信號(hào)。

發(fā)送幀的CRC值也由發(fā)送控制邏輯計(jì)算,傳統(tǒng)的串行計(jì)算方法達(dá)不到要求的速率,這里采用并行CRC算法進(jìn)行計(jì)算,每個(gè)時(shí)鐘有效沿可以計(jì)算32位數(shù)據(jù),大大提高了數(shù)據(jù)吞吐量。

緩沖到緩沖流量控制也在發(fā)送控制邏輯中實(shí)現(xiàn)。發(fā)送控制邏輯維持一個(gè)計(jì)數(shù)器,表示當(dāng)前已發(fā)送但還未被確認(rèn)的幀的數(shù)目,每當(dāng)發(fā)送1幀,計(jì)數(shù)器加1;當(dāng)接收到 R_RDY原語信號(hào)時(shí),計(jì)數(shù)器減1。如果這個(gè)值小于配置寄存器中的BB_Credit值,則表示可以繼續(xù)發(fā)送幀;否則,表明目標(biāo)端口已經(jīng)沒有可用的接收緩沖區(qū),發(fā)送控制邏輯此時(shí)就不往外發(fā)出幀。

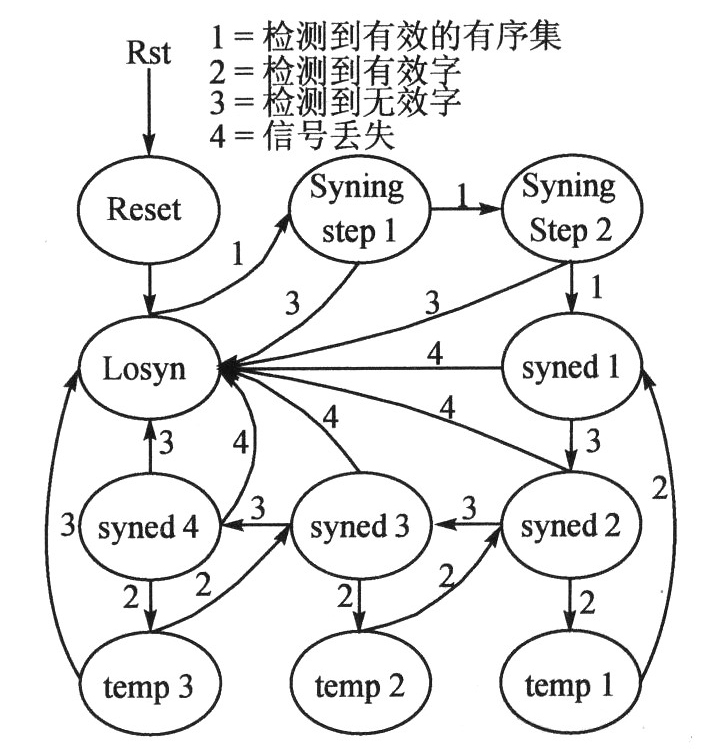

3.2接收控制邏輯

8B/10B解碼出來的數(shù)據(jù)是字節(jié)數(shù)據(jù),而所有的有序集都是字,因此需要在輸入的字節(jié)流中正確區(qū)分出字邊界。接收控制邏輯內(nèi)部的字同步模塊和接收狀態(tài)機(jī)協(xié)同工作,實(shí)現(xiàn)這一功能。標(biāo)準(zhǔn)規(guī)定的接收機(jī)狀態(tài)轉(zhuǎn)換圖如圖4所示。

圖4 接收機(jī)狀態(tài)轉(zhuǎn)換圖

3.38B/10B編解碼

傳統(tǒng)的編解碼方法由數(shù)字邏輯實(shí)現(xiàn),主要是為了節(jié)省邏輯資源。由于FPGA內(nèi)含有豐富的RAM,使其作為編解碼的載體既可以降低復(fù)雜程度又可以提高編解碼的速度,待編碼的數(shù)據(jù)作為地址線輸人,編碼數(shù)據(jù)存在RAM內(nèi)從數(shù)據(jù)線輸出。

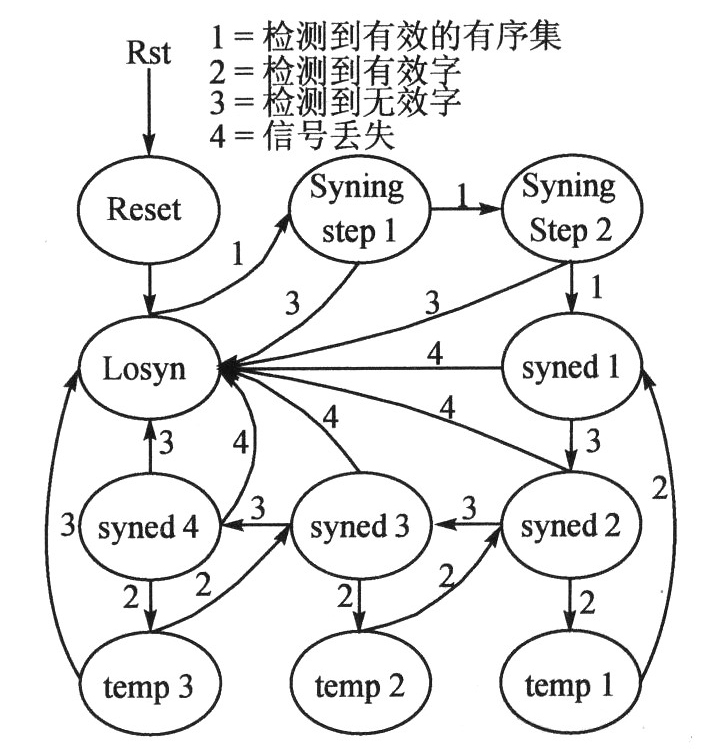

3.4端口狀態(tài)機(jī)

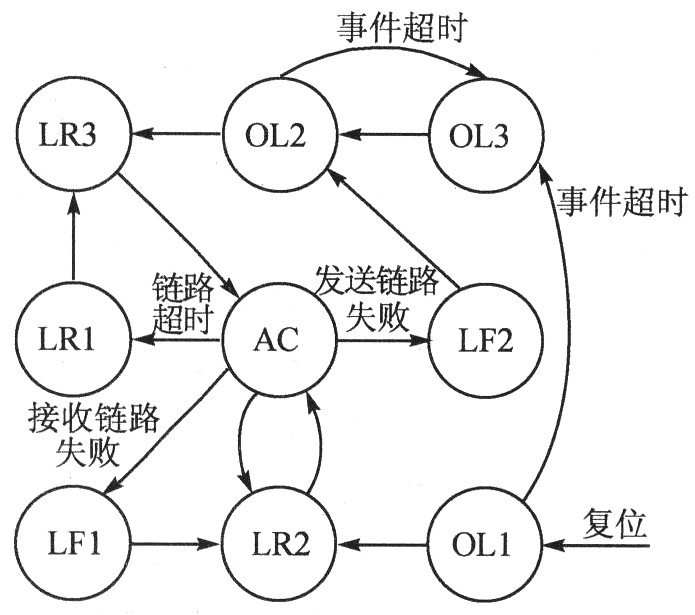

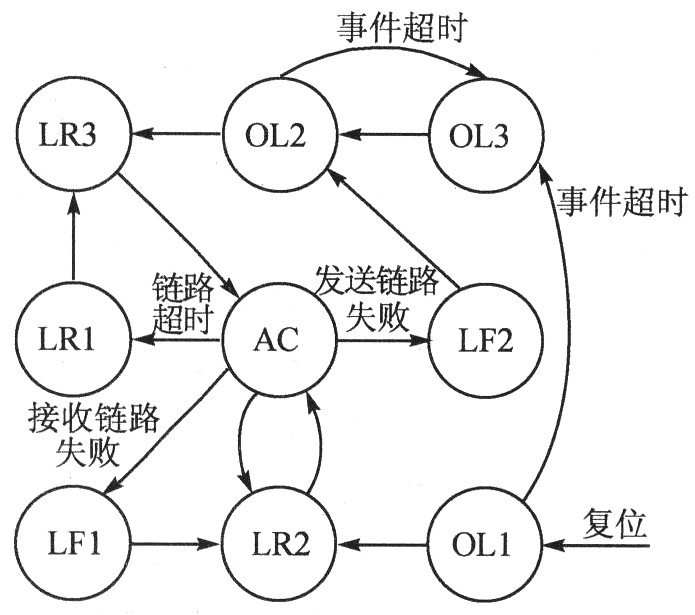

作為鏈路級(jí)差錯(cuò)檢測(cè)與恢復(fù)的核心,端口狀態(tài)機(jī)對(duì)收發(fā)鏈路的狀態(tài)進(jìn)行監(jiān)測(cè)。每當(dāng)鏈路狀態(tài)出現(xiàn)異常,端口狀態(tài)機(jī)就根據(jù)異常的起因啟動(dòng)不同的鏈路恢復(fù)協(xié)議來對(duì)鏈路進(jìn)行恢復(fù)。如果恢復(fù)失敗,那么端口狀態(tài)機(jī)就通過狀態(tài)寄存器向上層報(bào)告。出于版面的考慮,簡(jiǎn)化的端口狀態(tài)機(jī)的狀態(tài)轉(zhuǎn)換圖如圖5所示。

圖5 端口狀態(tài)機(jī)狀態(tài)轉(zhuǎn)換圖

3.5其他模塊

異步FIFO:由于接口控制芯片的接收部分使用從接收數(shù)據(jù)中恢復(fù)出來的時(shí)鐘,因此和芯片的主時(shí)鐘是異步的。當(dāng)將接收到的數(shù)據(jù)交給其他工作于主時(shí)鐘的模塊處理時(shí)需要進(jìn)行速率調(diào)整。異步FIFO用于實(shí)現(xiàn)這個(gè)功能。串并/并串轉(zhuǎn)換:高速的串并轉(zhuǎn)換對(duì)器件性能有較高要求。FPGA內(nèi)部集成了專用的硬核 (RocketIO)用來實(shí)現(xiàn)這一功能,因此對(duì)其進(jìn)行適當(dāng)?shù)呐渲眉纯伞_@樣節(jié)省了專用的串并轉(zhuǎn)換芯片。

配置寄存器存儲(chǔ)一系列的工作參數(shù),如(R_T_TOV、E_D_TOV等),復(fù)位后以默認(rèn)值初始化寄存器。完成注冊(cè)后,使用新值更新寄存器。

光纖通道傳輸核通過狀態(tài)寄存器來表示自己當(dāng)前所處的狀態(tài)(如在線、離線等)。

4.軟件設(shè)計(jì)

接口控制芯片的軟件部分負(fù)責(zé)進(jìn)行參數(shù)協(xié)商和處理與端到端數(shù)據(jù)傳輸相關(guān)的事務(wù),包括端口注冊(cè)和交換注冊(cè)、提供不同類型的服務(wù)、端到端流量控制、序列級(jí)差錯(cuò)檢測(cè)和恢復(fù)。

為了簡(jiǎn)化軟件的設(shè)計(jì),以嵌人式Linux操作系統(tǒng)作為接口控制芯片的軟件運(yùn)行環(huán)境。通過設(shè)計(jì)一系列的操作函數(shù),實(shí)現(xiàn)整個(gè)軟件系統(tǒng)。最重要的函數(shù)包括:端口注冊(cè)函數(shù)、IU發(fā)送函數(shù)和接收幀處理函數(shù)。

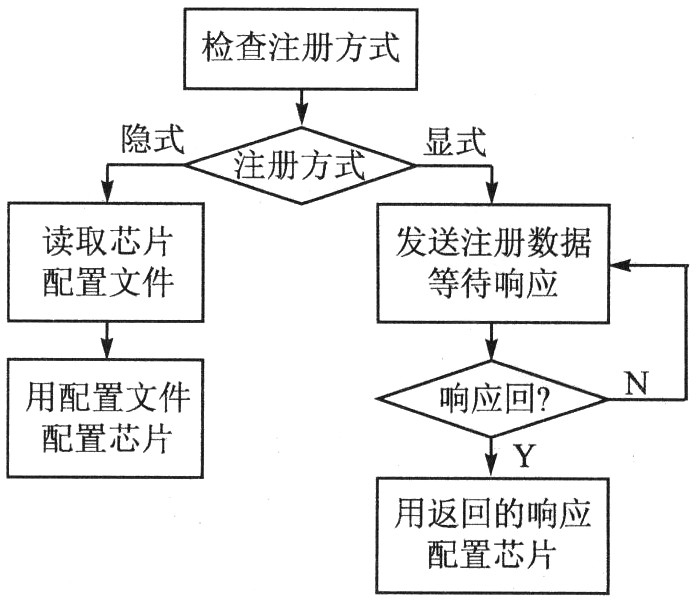

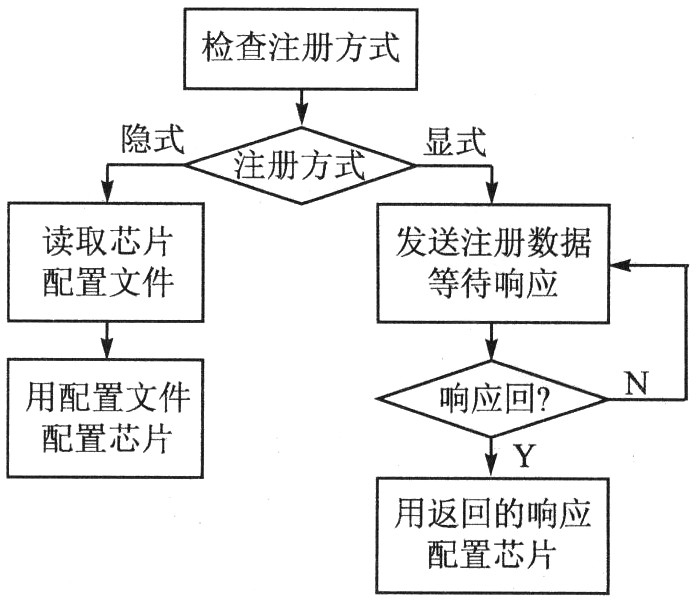

4.1端口注冊(cè)函數(shù)PLogin_in()

注冊(cè)包含端口注冊(cè)和交換注冊(cè)。兩種注冊(cè)的流程類似,這里僅分析端口注冊(cè)。系統(tǒng)啟動(dòng)后,需要對(duì)芯片的工作參數(shù)進(jìn)行配置,注冊(cè)函數(shù)根據(jù)用戶的配置選擇注冊(cè)方式。如果用戶指定隱式注冊(cè),那么注冊(cè)函數(shù)從配置文件中讀取默認(rèn)配置參數(shù)配置芯片;如果用戶指定顯式注冊(cè),那么注冊(cè)函數(shù)發(fā)送注冊(cè)請(qǐng)求,等對(duì)方端口返回響應(yīng)后,注冊(cè)函數(shù)用響應(yīng)的數(shù)據(jù)配置參數(shù)。端口注冊(cè)函數(shù)的工作流程如圖6所示。

圖6 IU注冊(cè)流程

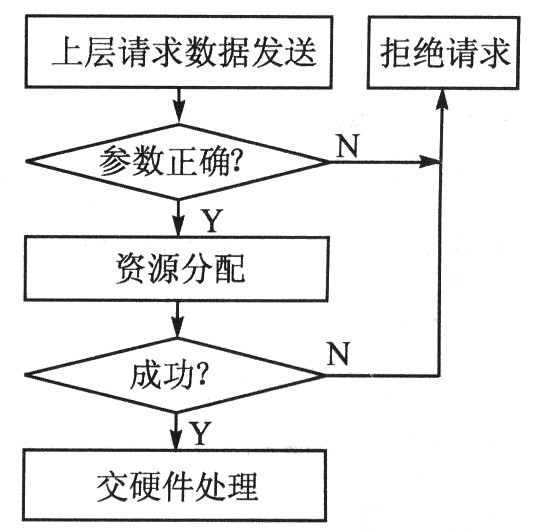

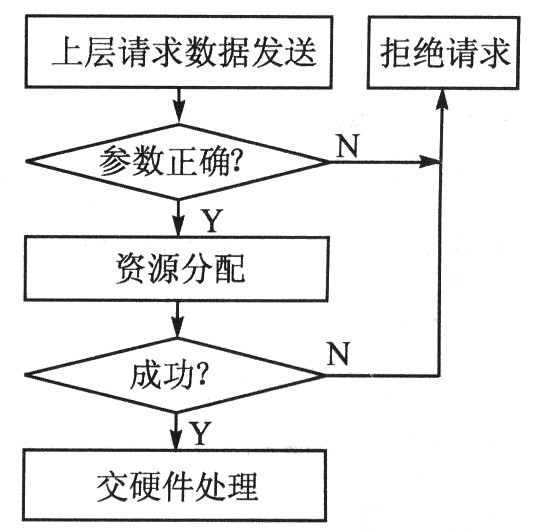

4.2IU發(fā)送函數(shù)Sen

圖7 IU發(fā)送流程

4.3接收幀處理函數(shù)Frm_Rcved()

當(dāng)光纖通道傳輸核將正確的幀接收到并存儲(chǔ)于接收緩沖區(qū)后,通過狀態(tài)接口通知PowerPC。此時(shí)Frm_Rcved()函數(shù)開始處理幀頭,幀頭中需要檢查的參數(shù)很多,這里不在贅述。如果幀頭中的參數(shù)沒有錯(cuò)誤,那么函數(shù)為這個(gè)新接收到的幀分配存儲(chǔ)空間,然后從接收緩沖區(qū)中將幀取到存儲(chǔ)器中,并以一定的方式和之前接收到的幀關(guān)聯(lián)起來(例如鏈表);如果幀頭中的參數(shù)有誤,則將幀丟棄并啟動(dòng)中止序列協(xié)議進(jìn)行序列恢復(fù)。

結(jié)語

本文總結(jié)了基于FPGA的光纖通道接口控制芯片設(shè)計(jì)方案,采用Verilog實(shí)現(xiàn)了接口控制芯片的RTL設(shè)計(jì)并完成了功能仿真和驗(yàn)證,并通過嵌入式PowerPC完成了接口控制芯片的控制軟件設(shè)計(jì);以Xilinx公司的Virtex-II Pro系列FPGA為平臺(tái),實(shí)現(xiàn)了接口控制芯片原型。該設(shè)計(jì)具有極大的靈活性和可擴(kuò)展性,在不同的應(yīng)用環(huán)境中只需要對(duì)相應(yīng)的軟硬件代碼進(jìn)行適當(dāng)?shù)牟脺p或擴(kuò)展即可,無需對(duì)PCB電路進(jìn)行任何更改,具有極其廣泛的應(yīng)用價(jià)值。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280