目前,國內(nèi)外廣泛使用的密碼處理芯片大都是實(shí)現(xiàn)某種特定密碼算法的專用芯片,如MD5芯片、SHA一1芯片等。由于專用密碼芯片實(shí)現(xiàn)的密碼算法是確定的且不可更改的,因此難以滿足不同密碼用戶多層次的安全性需要。為克服這一缺陷,本文介紹了SHA一1、SHA224及SHA256三種安全雜湊算法的基本流程,采用可重構(gòu)體系結(jié)構(gòu)的設(shè)計(jì)思想和方法設(shè)計(jì)出一款可實(shí)現(xiàn)這三種算法的可重構(gòu)密碼芯片,并對關(guān)鍵路徑進(jìn)行了優(yōu)化設(shè)計(jì)。最后給出了基于Ahera公司的Cyclone系列FPGA的可重構(gòu)密碼芯片的實(shí)現(xiàn)結(jié)果。

1.算法簡介

1.1SHA-1算法介紹

SHA-1算法輸入報(bào)文的最大長度不超過264bit,輸入按512bit分組進(jìn)行處理,產(chǎn)生的輸出是一個160bit的報(bào)文摘要。該算法處理包括以下幾個步驟:

(1)附加填充比特。對報(bào)文進(jìn)行填充使報(bào)文長度與448模512同余(長度=48 mod 512),填充的比特?cái)?shù)范圍從1到512,填充比特串的最高位為1,其余位為0。

(2)附加長度值。將用64bit表示的初始報(bào)文(填充前)的位長度附加在步驟(1)的結(jié)果后(低位字節(jié)優(yōu)先)。

(3)初始化緩存。使用一個160bit的緩存存放該散列函數(shù)的中間值及最終結(jié)果。該緩存的值分別表示為A=67452301。B=EFCDAB89,C=0x98BADCEF,D=0x10325476,E=C3D2E1F0。

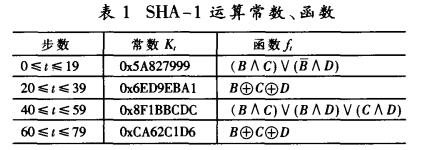

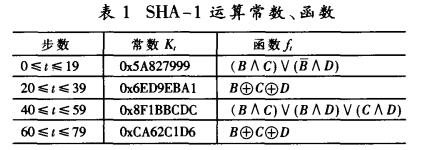

(4)處理512bit(16個字)報(bào)文分組序列。算法的核心是一個包含四個循環(huán)的模塊,每個循環(huán)由20個處理步驟組成。四個循環(huán)有相似的結(jié)構(gòu),但每個循環(huán)使用不同的邏輯函數(shù),分別表示為f1、f2、f3、f4。每個循環(huán)都以當(dāng)前正在處理的512bit和160-bit緩存值A(chǔ)、B、C、D、E為輸入,然后更新緩存內(nèi)容。每個循環(huán)還使用一個額外的常數(shù)值,對應(yīng)的四輪Kt取值及邏輯函數(shù)ft如表1所示。第四循環(huán)最后一步的輸出與第一循環(huán)的輸入進(jìn)行模232相加后得到下一個512bit分組計(jì)算所需的A、B、C、D、E值。

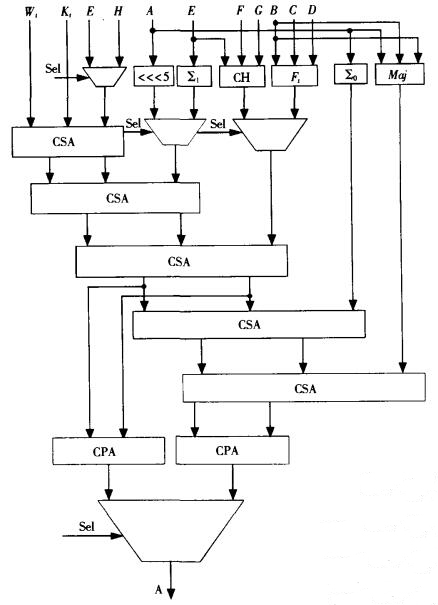

(5)所有的512bit分組處理完畢后,最后一個分組產(chǎn)生的輸出便是160bit的報(bào)文摘要。圖1說明了SHA一1算法中每一處理步驟所包含的操作。

圖1 基本的SHA-1操作(單步)

1.2SHA-224/SHA-256算法介紹

SHA-224/SHA-256算法輸入報(bào)文的最大長度不超過264bit,輸入按512bit分組進(jìn)行處理,產(chǎn)生的輸出是一個224bit或256bit的報(bào)文摘要。該算法處理包括以下幾個步驟:

(1)和(2)與SHA-1算法的前兩步相同。

(3)初始化緩存。使用一個256bit的緩存存放該散列函數(shù)的中間值及最終結(jié)果。當(dāng)執(zhí)行SHA-224算法時,該緩存的值分別表示為A=0xC1059ED8,B=0x367CD507,C=0x3070DD17,D=0xF70E5939,E=0xFFC00B31,F(xiàn)=0x68581511,G=0x64F98FA7,H=0xBEFA4FA4;當(dāng)執(zhí)行SHA一256算法時,該緩存的值分別表示為:A=0x6A09E667=0xBB67AE85,C=0x3C6EF372,D=0xA54FF53A,E=0x510E527F,F(xiàn)=0x9B05688C,G=0x1F83D9AB,H=0x5BEOCD19。

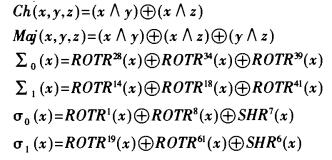

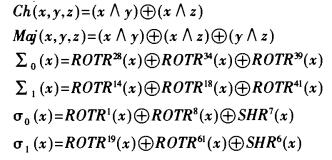

(4)處理512bit(16個字)報(bào)文分組序列。該算法使用六種基本邏輯函數(shù),由64步迭代運(yùn)算組成。每步都以256bit緩存值A(chǔ)、B、C、D、E、F、G、H為輸入,然后更新緩存內(nèi)容。每步使用一個32bit常數(shù)值Kt和一個32bitWt。六種基本函數(shù)如下:

Wt是由當(dāng)前的輸入分組(512bit長)導(dǎo)出的32bit長的數(shù)。在所有64次運(yùn)算完成之后,將其輸出A、B、C、D、E、F、G、H與第一步的輸入A、B、C、D、E、F、G、H的值對應(yīng)進(jìn)行模232相加。然后將其結(jié)果作為下一分組數(shù)據(jù)A、B、C、D、E、F、G、H的值繼續(xù)運(yùn)行算法。

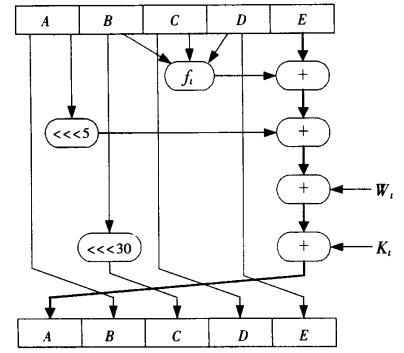

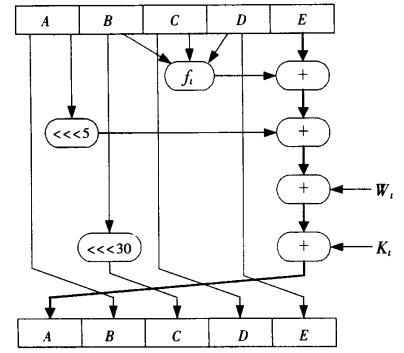

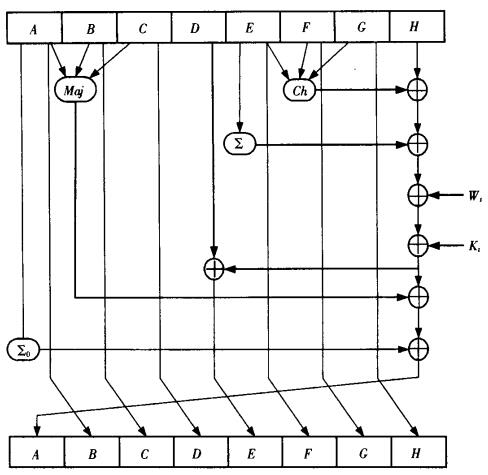

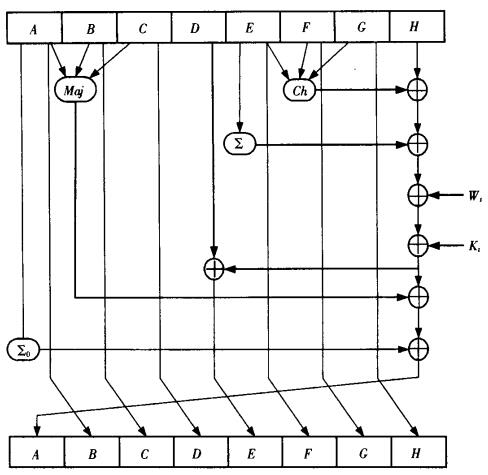

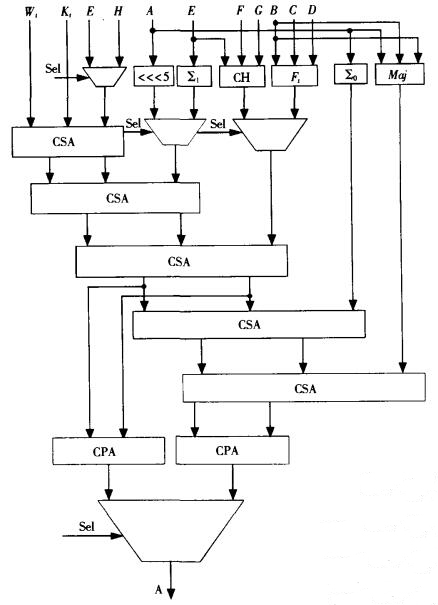

(5)所有的512bit分組處理完畢后,對于SHA256算法,最后一個分組產(chǎn)生的輸出便是256bit的報(bào)文摘要;若是SHA-224算法,則最后一個分組產(chǎn)生的輸出取前224bit作為報(bào)文摘要。圖2說明了SHA-224/SHA-256算法每一處理步驟所包含的操作。

圖2 基本的SHA-224/SHA-256單步運(yùn)算

2.電路結(jié)構(gòu)

2.1總體結(jié)構(gòu)設(shè)計(jì)

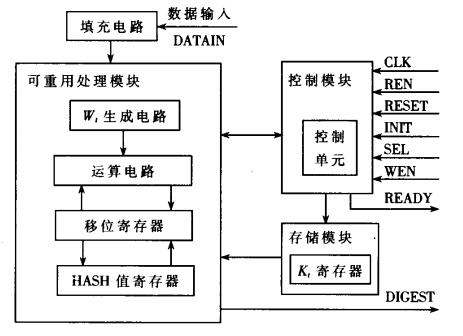

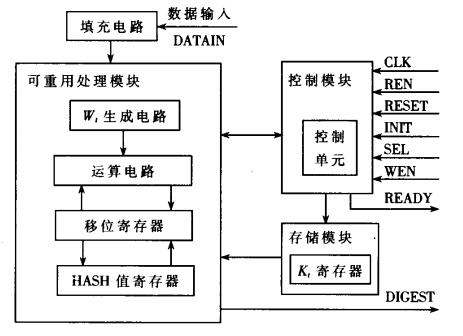

本設(shè)計(jì)采用可重構(gòu)密碼芯片的設(shè)計(jì)思想,通過對SHA-1、SHA-224、SHA-256三種算法分析可以看出,這三種算法的Wt生成電路和移位存儲模塊是可重用的部件。數(shù)據(jù)通路中的CSA加法器、存放雜湊值的移位寄存器以及常數(shù)值存儲模塊K也都是可重用的部件。按照上述分析,把該芯片分為三大模塊:存儲模塊、控制模塊、可重用處理模塊。其中,存儲模塊用于存儲各種算法所需的常數(shù)值。控制模塊用于接收外部的控制信號和選擇算法信號,控制各種算法的存儲和運(yùn)算。可重用處理模塊用于對各種算法進(jìn)行可重構(gòu)計(jì)算。根據(jù)整體算法要求,又將其再往下劃分為七個功能子模塊。本設(shè)計(jì)充分利用FPGA可重構(gòu)計(jì)算的特點(diǎn),對可重用的模塊進(jìn)行可重構(gòu)計(jì)算以實(shí)現(xiàn)對FPGA資源的靈活有效利用。SHA-1/SHA-224/SHA-256可重構(gòu)運(yùn)算電路IPCORE由以下七個子模塊構(gòu)成:控制電路、Wt生成電路、Kt常數(shù)寄存器、填充電路、運(yùn)算電路、HASH值暫存寄存器、移位寄存器。本設(shè)計(jì)總體結(jié)構(gòu)框圖如圖3所示。

圖3 SHA-1/SHA-224/SHA-256可重構(gòu)芯片電路設(shè)計(jì)整體架構(gòu)

其中,Kt常數(shù)寄存器子模塊和HASH值暫存寄存器子模塊屬于存儲模塊;Wt生成電路子模塊、填充電路子模塊、運(yùn)算電路子模塊、移位寄存器子模塊屬于可重用處理模塊。控制電路子模塊屬于控制模塊。每個子模塊具體功能為:Wt生成電路負(fù)責(zé)對每組512bit的輸入數(shù)據(jù)生成64個或80個32bit的字并送入運(yùn)算通路。Kt常數(shù)寄存器用于存儲64個或80個32bit的常量。控制電路負(fù)責(zé)接收外部的控制信號,并產(chǎn)生所有的內(nèi)部控制信號,采用計(jì)數(shù)器電路生成。填充電路接收輸入數(shù)據(jù),產(chǎn)生每個512bit分組并送入Wt生成電路。運(yùn)算電路負(fù)責(zé)計(jì)算多個模232加法。然后將其結(jié)果送入移位寄存器。HASH值暫存寄存器用于存儲5個或8個32bit寄存器的初始值以及每個512bit分組運(yùn)算完畢后的5個或8個32bit寄存器的臨時值。移位寄存器負(fù)責(zé)對每步運(yùn)算的數(shù)據(jù)進(jìn)行移位存儲。當(dāng)HASH運(yùn)算結(jié)束時,移位寄存器將其本身值與HASH值暫存寄存器中的值相加。當(dāng)外部讀信號有效時,電路實(shí)現(xiàn)串行移位功能,在控制信號作用下,將寄存器內(nèi)的數(shù)據(jù)順序讀出。

CLK是系統(tǒng)時鐘信號;RESET是復(fù)位信號,RESET有效時,所有寄存器復(fù)位;INIT是初始化信號,INIT有效時,初始化摘要計(jì)算,在每一批數(shù)據(jù)進(jìn)行摘要運(yùn)算之前,首先執(zhí)行初始化操作,然后按512bit分組寫入數(shù)據(jù);WEN是寫使能信號,WEN有效時,在CLK時鐘上升沿將512bit的數(shù)據(jù)分16次由32bit數(shù)據(jù)總線寫入芯片內(nèi)部數(shù)據(jù)寄存器;REN是讀使能信號,REN有效時,將內(nèi)部運(yùn)算結(jié)果讀出數(shù)據(jù)端口;DATAIN是數(shù)據(jù)輸入,即輸入的512bit分組數(shù)據(jù)。SEL是選擇算法指令信號,用來選擇所需的算法。READY是運(yùn)算狀態(tài)信號,每512bit分組運(yùn)算完畢后,READY變?yōu)橛行В却x出或外部數(shù)據(jù)繼續(xù)輸入。DIGEST是摘要值輸出,即REN信號有效時輸出的相應(yīng)摘要值。

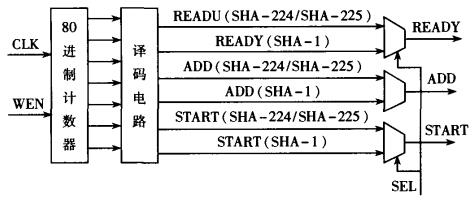

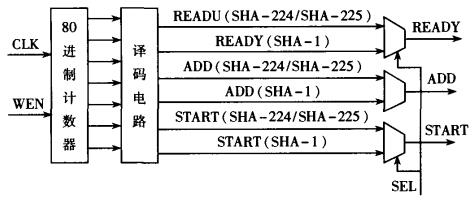

2.2控制電路設(shè)計(jì)

控制電路的核心是一個7位計(jì)數(shù)器,每來一個時鐘信號,便進(jìn)行加1操作,根據(jù)不同的計(jì)數(shù)值可給出不同的控制信號。依照算法要求,每處理一組5l2bit分組數(shù)據(jù)時,若執(zhí)行SHA-1算法則需要80步運(yùn)算;若執(zhí)行SHA-224/SHA-256算法則需要64步。為實(shí)現(xiàn)邏輯資源的可重構(gòu),達(dá)到計(jì)數(shù)器資源重用的目的,就需要計(jì)數(shù)器在不同的算法下產(chǎn)生不同的控制信號。本控制電路采用增加選擇算法信號(SEL)來實(shí)現(xiàn),其結(jié)構(gòu)如圖4所示。其中READY信號表示每一分組運(yùn)算完成信號。ADD信號表示分組運(yùn)算的最后一步各寄存器的值與第一步計(jì)算時的各寄存器的輸入值相加信號。START信號表示移位寄存器移位信號。

圖4 SHA-1/SHA-224/SHA-256控制電路設(shè)計(jì)

2.3數(shù)據(jù)路徑優(yōu)化設(shè)計(jì)

SHA-1運(yùn)算模塊使用五個寄存器(見圖1)存放散列函數(shù)每一步運(yùn)算的中間結(jié)果;SHA-224/SHA-256運(yùn)算模塊則采用八個寄存器(見圖2)存放散列函數(shù)每一步運(yùn)算的中間結(jié)果。為實(shí)現(xiàn)可重構(gòu)計(jì)算以使不同算法邏輯單元重用,本設(shè)計(jì)采用八級移位寄存器A、B、C、D、E、F、G、H實(shí)現(xiàn),每個寄存器32bit位寬。當(dāng)執(zhí)行SHA一1算法時,使用前五個32bit移位寄存器;當(dāng)執(zhí)行SHA-224/SHA-256算法時,使用全部八個移位寄存器。當(dāng)RESET信號有效時,寄存器初始化,電路將根據(jù)不同算法給寄存器賦初值。數(shù)據(jù)路徑設(shè)計(jì)的關(guān)鍵是計(jì)算每步A寄存器的值。當(dāng)執(zhí)行SHA-1算法時,At+1=(Et+ft(Bt,Ct,Dt)+At(<<<5)+Wt+Kt)mod232;當(dāng)執(zhí)行SHA-224/SHA-256算法時:At+1=(Ht+∑t(Et)+Ch(Et,F(xiàn)t,Gt)+Kt+Wt+∑0(At)+Maj(At,Bt,Ct)mod232

式中:At、Bt、Ct、Dt、Et、Ft、Gt、Ht、Wt、Kt是第t時刻的各寄存器的值、消息分組和常數(shù)值。At+1是第t+1時刻的A寄存器的值。

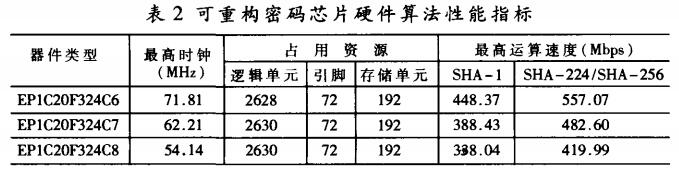

SHA-1/SHA-224/SHA-256運(yùn)算模塊的關(guān)鍵路徑的設(shè)計(jì)是計(jì)算At+1,在這一路徑中,需要完成多個多變量邏輯函數(shù)和多個連續(xù)32位加法的運(yùn)算。可以看出,At+1計(jì)算主要包括非線性函數(shù)運(yùn)算、加法運(yùn)算和移位。其中非線性函數(shù)運(yùn)算只是完成信號在不同輸入輸出之間的切換,只需用組合邏輯電路設(shè)計(jì),不會產(chǎn)生太大的延遲;移位只占用布線資源,同樣不會對電路的速度有影響;而加法運(yùn)算由于進(jìn)位會在電路上產(chǎn)生延遲,因此應(yīng)盡量對其進(jìn)行優(yōu)化,否則會影響電路運(yùn)算速度。因此在電路的設(shè)計(jì)上采用保存進(jìn)位加法器(CSA),以減少延遲。由于SHA-1算法執(zhí)行的是五個連續(xù)32位加法,而SHA-224/SHA-256執(zhí)行的是七個連續(xù)32位加法,而且SHA-1與SHA-224/SHA-256所使用的邏輯函數(shù)和輸入寄存器的值不同,這就需要將各個不同的函數(shù)變換的值提前計(jì)算出來,再根據(jù)選擇的算法對不同的值進(jìn)行選擇,然后送入CSA加法器的輸入端。

本設(shè)計(jì)電路由五級保存進(jìn)位加法器(CSA)和兩個串行進(jìn)位加法器(CPA)構(gòu)成,實(shí)現(xiàn)了保存進(jìn)位加法器對不同算法的重用,其結(jié)構(gòu)如圖5所示。

圖5 連加運(yùn)算優(yōu)化電路

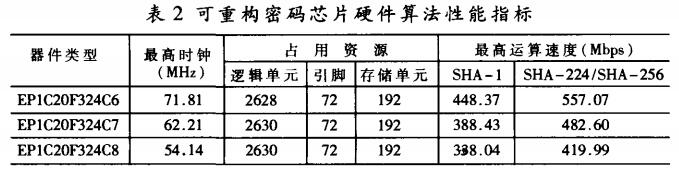

3.性能評估

以上設(shè)計(jì)采用VHDL語言描述,在QuartusII 4.2環(huán)境下編譯綜合,選用Altera Cyclone系列器件為目標(biāo)器件進(jìn)行整體綜合、仿真和底層布局,采用FIPS180-2給出的測試數(shù)據(jù)進(jìn)行仿真,采用單個分組和多個分組分別進(jìn)行測試,均得到正確結(jié)果。

在本設(shè)計(jì)中,當(dāng)電路執(zhí)行SHA-1算法時運(yùn)算一個512bit分組需要82個時鐘周期,其中第一個為數(shù)據(jù)準(zhǔn)備周期,第2~81個為運(yùn)算周期,第82個為移位寄存器的值與HASH值暫存寄存器的值相加并將其結(jié)果送入移位寄存器的周期;當(dāng)執(zhí)行SHA-224/SHA-256算法時運(yùn)算一個512bit分組需要66個時鐘周期,其中第一個為數(shù)據(jù)準(zhǔn)備周期,第2~65個周期為運(yùn)算周期,第66為移位寄存器的值與HASH值暫存寄存器的值相加并將其結(jié)果送入移位寄存器的周期。該模塊的運(yùn)算速度可以通過下面公式得出:

運(yùn)算速度=(分組長度/運(yùn)算耗用的時鐘周期數(shù))×系統(tǒng)時鐘頻率,單位為Mbps

將實(shí)現(xiàn)的可重構(gòu)算法分別下載到Altera Cyclone系列器件后測得的主要性能指標(biāo)在表2中給出。

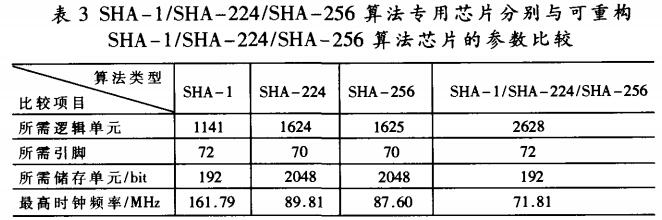

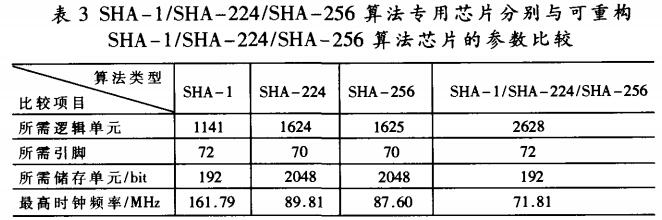

本設(shè)計(jì)的創(chuàng)新點(diǎn)是利用可重構(gòu)設(shè)計(jì)思想對SHA-1、SHA-224、SHA-256三種不同算法的可重用模塊進(jìn)行可重構(gòu)計(jì)算,通過FPGA實(shí)現(xiàn)時既能靈活實(shí)現(xiàn)不同算法,又能實(shí)現(xiàn)資源的充分利用,節(jié)約大量邏輯資源。為進(jìn)一步說明本設(shè)計(jì)對FPGA資源利用情況,下面將這三種算法的專用芯片與可重構(gòu)SHA-1/SHA-224/SHA-256算法芯片的一些參數(shù)進(jìn)行比較,如表3所示。這里要說明的是這三種算法的參數(shù)均是采用類似SHA-1/SHA-224/SHA-256的總體電路架構(gòu)設(shè)計(jì)得到的。選擇的器件均是EP1C20F324C6。

結(jié)束語

本文總結(jié)了基于FPGA的可重構(gòu)密碼芯片設(shè)計(jì)方案。該可重構(gòu)密碼芯片是一種創(chuàng)新性的密碼芯片,它很好地克服了傳統(tǒng)的密碼芯片只能實(shí)現(xiàn)特定密碼算法的弊端,使得密碼使用者能夠在它上面很方便地選擇所需要的密碼算法,從而大大提高了密碼系統(tǒng)的靈活性。可重構(gòu)密碼芯片可作為構(gòu)建密碼系統(tǒng)的核心部件而廣泛應(yīng)用于保密通信、網(wǎng)絡(luò)終端加密設(shè)備等領(lǐng)域,因此該研究方向具有重要的政治、軍事和經(jīng)濟(jì)意義。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280